## **Refined EVLA WIDAR Correlator Architecture**

NRC-EVLA Memo# 014

Brent Carlson, October 2, 2001

National Research Council of Canada, Herzberg Institute of Astrophysics

#### **ABSTRACT**

This memo is a technical blueprint for further development of the WIDAR correlator for the EVLA. This document is not intended for the casual reader, and the assumption is made that the reader is familiar with all of the preceding memos in this series, and with correlator signal processing. In some sections, particularly concerning the Baseline Board, many functional and performance details are included to provide a concrete baseline plan for implementation. This helps to establish a high level of confidence that some of the more 'exotic' correlator functions can indeed be realized. In other sections, less detail is provided since functionality is reasonably straightforward.

The concepts presented in this document were developed over a period of about two years with valuable input and feedback from many NRAO engineers, scientists, and users during several meetings. Nothing in this document is 'etched in stone', but it presents at least one coherent plan so that correlator development can proceed to its next phase of implementation.

## **Table of Contents**

| 1 | EXECUTIVE SUMMARY OF CORRELATOR CAPABILITIES                        | 11 |

|---|---------------------------------------------------------------------|----|

| 2 | SYSTEM OVERVIEW                                                     | 12 |

|   | 2.1 Flexibilities                                                   | 14 |

| 3 | STATION BOARD                                                       | 16 |

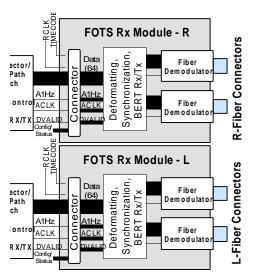

|   | 3.1 FOTS Rx Module(s)                                               | 17 |

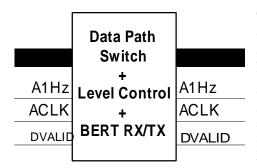

|   | 3.2 Data Path Switch                                                |    |

|   | 3.3 COARSE DELAY MODULE                                             |    |

|   | 3.4 Fine Delay Controller                                           |    |

|   | 3.5 WIDEBAND AUTOCORRELATOR                                         |    |

|   | 3.6 Delay Generator                                                 |    |

|   | 3.7 FIR FILTER BANKS                                                | 21 |

|   | 3.7.1 Sub-band Multi-beaming                                        | 22 |

|   | 3.7.2 7-bit Requantization and Correlation                          | 24 |

|   | 3.8 OUTPUT CROSS-BAR SWITCH AND PULSAR TIMING                       |    |

|   | 3.9 FORMATTING AND TIMING                                           | 25 |

|   | 3.10 MISCELLANEOUS FUNCTIONS                                        | 26 |

| 4 | BASELINE BOARD                                                      | 27 |

|   | 4.1 RECIRCULATION CONTROLLER                                        | 30 |

|   | 4.1.1 Signal Descriptions                                           |    |

|   | 4.1.1.1 Inputs from Station Boards                                  |    |

|   | 4.1.1.2 Outputs to Correlator Chips                                 |    |

|   | 4.1.2 Simplified Block Diagram                                      |    |

|   | 4.1.3 Input Timing and Synchronization                              |    |

|   | 4.1.4 Recirculation                                                 |    |

|   | 4.1.4.1 Timestamps                                                  |    |

|   | 4.1.4.2 Wide-band Recirculation                                     |    |

|   | 4.1.5.1 Recirculation Real-Time Control                             |    |

|   | 4.1.5.2 Normal Dumping Real-Time Control                            |    |

|   | 4.1.5.3 Pulsar Phase Binning Real-Time Control                      |    |

|   | 4.1.5.4 Pulsar Phase Binning and Recirculation Real-Time Control    |    |

|   | 4.2 CORRELATOR CHIP                                                 |    |

|   | 4.2.1 Simplified Functional Description                             |    |

|   | 4.2.2 Detailed Functional Description                               | 54 |

|   | 4.2.2.1 Black-Box Correlator Chip Diagram                           |    |

|   | 4.2.2.2 Correlator Chip Block Diagram                               |    |

|   | 4.2.2.2.2 SID/SBID/BBID Capture                                     |    |

|   | 4.2.2.2.3 VLBI Mode Phase Modifier and Vernier Delay Generator      |    |

|   | 4.2.2.2.4 Readout Controller/LTA Interface                          |    |

|   | 4.2.2.2.5 4X CCQ Lag Correlator Array                               |    |

|   | 4.3 LTA CONTROLLER                                                  |    |

|   | 4.3.1 Black-Box Description and the Front Panel Data Port Interface |    |

|   | 4.3.1.1 Output Data Frame Formats                                   |    |

|   | 4.3.2 Detailed LTA Controller Functional Description                |    |

|   | 4.4 FPDP SCHEDULER FPGA                                             |    |

| _ | 4.5 BASELINE BOARD PHYSICAL LAYOUT                                  |    |

| 5 |                                                                     |    |

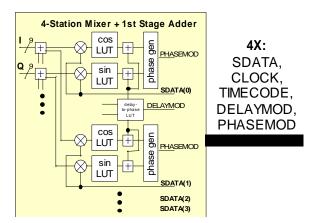

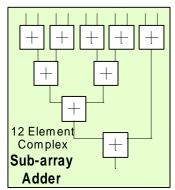

|   | 5.1 4-STATION MIXER AND 1 <sup>ST</sup> STAGE ADDER                 | 85 |

|   | 5.2 | 2 <sup>nd</sup> Stage Sub-Array Adder | 86  |

|---|-----|---------------------------------------|-----|

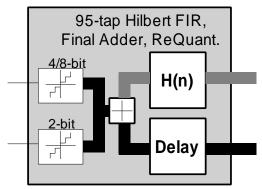

|   | 5.3 | HILBERT FIR                           | 86  |

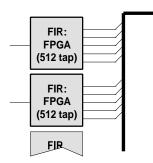

|   | 5.4 | SUB-SUB-BAND FIR FILTER BANK          | 87  |

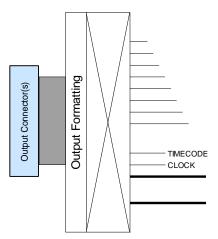

|   | 5.5 | OUTPUT SWITCH AND FORMATTING          | 87  |

|   | 5.6 | ERROR DETECTION                       | 87  |

| 6 | N   | /IISCELLANEOUS MODULES                | 89  |

|   | 6.1 | SUB-BAND DISTRIBUTOR BACKPLANE        | 89  |

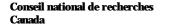

|   | 6   | .1.1 MDR-80 Connector Pin Assignments | 90  |

|   | 6.2 | STATION DATA FANOUT BOARD             |     |

|   | 6.3 | BASELINE ENTRY BACKPLANE              | 94  |

|   | 6.4 | PHASING BOARD ENTRY BACKPLANE         | 95  |

|   | 6.5 | TIMECODE GENERATOR BOX                |     |

|   | 6.6 | OTHER MODULES                         | 96  |

| 7 | S   | YSTEM DESIGN                          | 98  |

|   | 7.1 | SUB-RACK AND RACK DESIGN              | 98  |

|   | 7.2 | REMOTE POWER CONTROL AND MONITORING   |     |

|   | 7.3 | CORRELATOR FLOOR PLAN                 | 102 |

|   | 7.4 | CORRELATOR COMPUTING                  | 105 |

|   | 7.  | .4.1 Hardware Configuration           | 105 |

|   | 7.  | .4.2 Software Configuration           |     |

| 8 | R   | REFERENCES                            | 108 |

# **List of Figures**

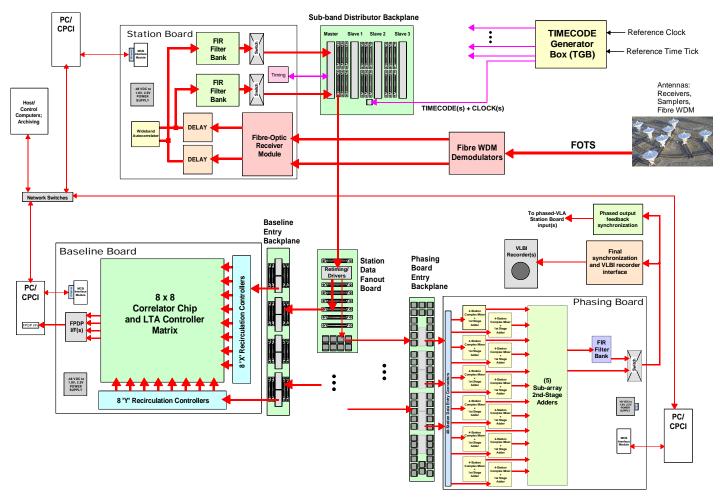

| Figure 2-1 Simplified correlator module connectivity diagram. The three main boards are the Station                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board, the Baseline Board, and the Phasing Board. Data and signal flows are as indicated by the red                                                                                                                    |

| arrows12                                                                                                                                                                                                               |

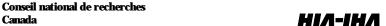

| Figure 3-1 Detailed Station Board functional block diagram. Data enters via the FOTS Rx Modules, is                                                                                                                    |

| delayed to compensate for wavefront delay, is filtered into sub-bands with digital filters, and then                                                                                                                   |

| exits via a switch for further processing. A detailed description of each block is given in the                                                                                                                        |

| following sub-sections                                                                                                                                                                                                 |

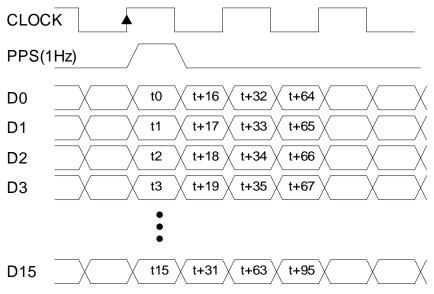

| synchronous to a clock provided to the mezzanine card. Time slot allocations are as indicated in the                                                                                                                   |

| figure and are bit times at the 4 Gs/s rate. Data at different rates will have different time slot                                                                                                                     |

| assignments. The PPS (1 Hz time tick) epoch is for t <sub>o</sub> alignment independent of time slot allocations                                                                                                       |

| or actual sampled data rates. This ensures that receiving circuitry and any necessary lower-rate shift                                                                                                                 |

| clock generation are always resynchronized every PPS                                                                                                                                                                   |

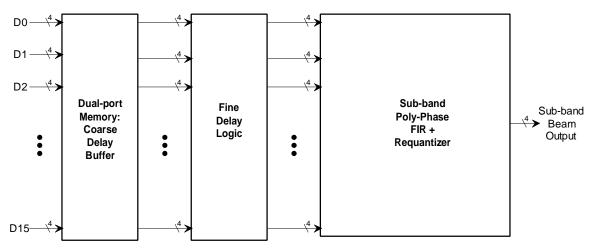

| Figure 3-3 FIR filter with additional elements required for sub-band multi-beaming. The on-chip Dual-                                                                                                                  |

| port Memory buffer performs coarse delay to within 16 samples at 4 Gs/sec and the Fine Delay Logic                                                                                                                     |

| performs delay to within +/-0.5 samples at 4 Gs/sec in a similar fashion to the baseband delay.                                                                                                                        |

| Restricting the sub-band beam offset to within $\sim 0.25^{\circ}$ of the baseband beam ensures that the on-chip delay buffer is small, and that the sub-band delay relative to the baseband delay is changing slowly. |

|                                                                                                                                                                                                                        |

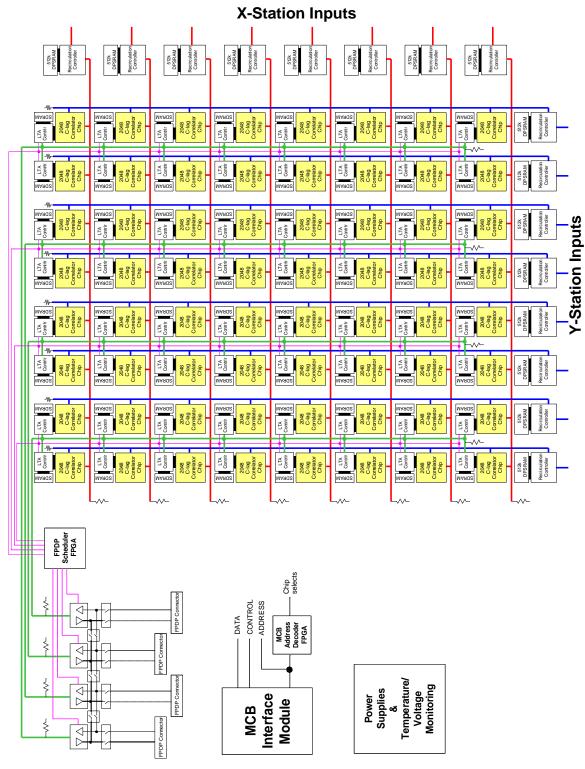

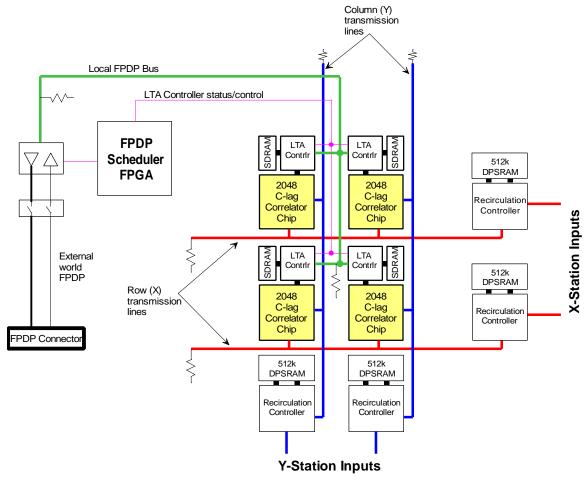

| <b>Figure 4-1</b> Baseline Board block diagram. The board consists of an 8x8 array of 64 custom 2048 lag                                                                                                               |

| correlator chips, fed by data from Recirculation Controller FPGAs. Each correlator chip is equipped                                                                                                                    |

| with its own LTA Controller that reads out data, saves it in dedicated LTA SDRAM and then, when                                                                                                                        |

| enabled by the FPDP Scheduler, becomes an FPDP transmit master to send the data out on up to 4                                                                                                                         |

| FPDP interfaces                                                                                                                                                                                                        |

| Figure 4-2 2x2 correlator chip 'slice' of the Baseline Board block diagram shown in Figure 4-1. Data                                                                                                                   |

| from a particular set of Station Boards arrives at a Recirculation Controller where it is modified and formatted for transmission to a row or column of correlator chips. On command from the                          |

| Recirculation Controller, the correlator chip dumps data and transmits it to a dedicated LTA                                                                                                                           |

| Controller that saves it in local SDRAM. Once LTA data is ready it is transmitted, when enabled by                                                                                                                     |

| the FPDP Scheduler FPGA, by the LTA Controller onto the local FPDP bus and finally onto the                                                                                                                            |

| external world FPDP via FPDP bus drivers                                                                                                                                                                               |

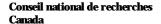

| Figure 4-3 Black-box diagram of the Recirculation Controller FPGA. Data, timing, and synchronization                                                                                                                   |

| information enter from Station Boards on the right. Data and information formatted for use by a row                                                                                                                    |

| or column of correlator chips exits on the left. Two, 256k x 18 DPSRAM memories are used in ping-                                                                                                                      |

| pong mode to provide an effective 512k x 18 recirculation memory that operates at a 256 MHz clock                                                                                                                      |

| rate. An MCB bus interface is shown, but the actual address space and word width requires further definition. Input signals from the Station Boards (and CLOCKO to the correlator chips) are LVDS                      |

| and all other signals are LVTTL.                                                                                                                                                                                       |

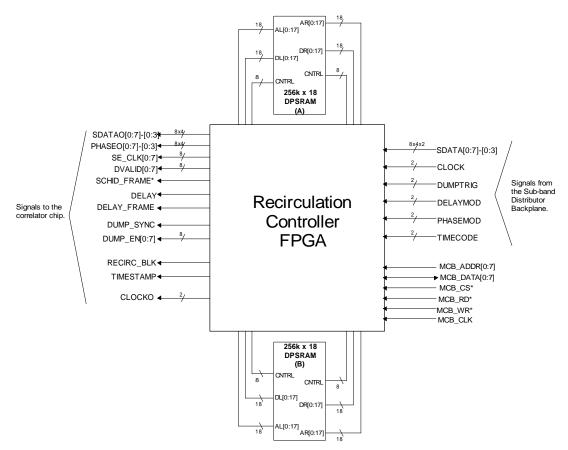

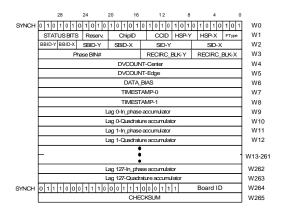

| Figure 4-4 Sampled data stream, SDATA, format. Each data stream contains embedded station ID                                                                                                                           |

| (SID[0:7]), sub-band ID (SBI[0:4]), and baseband ID (BBI[0:3]). Each <i>bit</i> stream also contains an                                                                                                                |

| embedded CRC-4 code that allows for continuous error checking—required during time-skew                                                                                                                                |

| removal and to monitor the integrity of the data link from the source. When present, this embedded                                                                                                                     |

| data will be recognized and flagged as data invalid by the Recirculation Controller when it is passed                                                                                                                  |

| on to the correlator chip—effectively blanking it from being correlated. However, because the                                                                                                                          |

| number of data valid counters in the correlator chip is restricted, this blanking can introduce small,                                                                                                                 |

| unwanted systematic effects (incorrect data valid counts at some lags). To allow for no blanking correlation (i.e. once synchronization and IDs are established), the 'C' bit (Control Bit) in                         |

| TIMECODE determines whether the embedded data is present or not. If the 'C' bit is 1, then                                                                                                                             |

| embedded data is present, if 0, then it is not                                                                                                                                                                         |

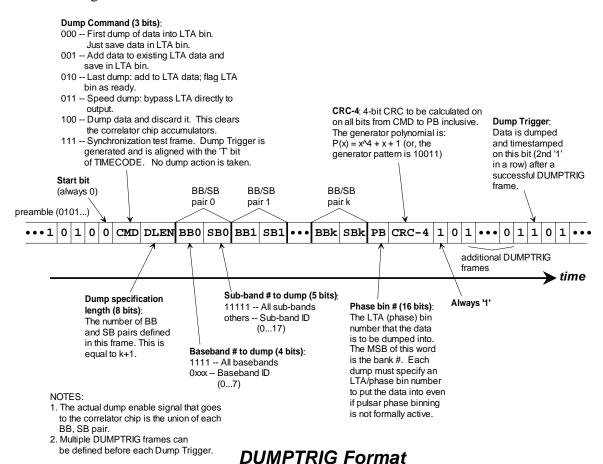

| Figure 4-5 DUMPTRIG format. DUMPTRIG consists of one or more frames that define one or more                                                                                                                            |

| dumps that are to occur, followed by the Dump Trigger that causes the actual dump to occur. This                                                                                                                       |

| format provides information that the Recirculation Controller needs to trigger dumps to the correlator                                                                                                                 |

| chip—and ultimately command the LTA controller as well. The CMD '111' (Synchronization test                                                                                                                            |

| frame) allows synchronization checks of DUMPTRIG to TIMECODE to occur even when dumping                                                                                                                                |

|   | s synchronized to a pulsar rather than system timing by inserting dummy frames. This is important o guarantee recirculation synchronization between 'X' and 'Y' Recirculation Controllers                             |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

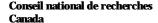

|   | e <b>4-6</b> DELAYMOD format. A 100-bit delay frame consists of 12 bits of delay information for each                                                                                                                 |

|   | baseband followed by a CRC-4 code calculated on all of the bits in the frame. Of the 12 bits of delay                                                                                                                 |

|   | nformation, 8 bits contains the fractional sample delay (2's complement in the range of $\pm 0.5$ samples                                                                                                             |

|   | information, 8 bits contains the fractional sample delay (2's complement in the range of $\pm 0.5$ samples of delay), and 4 bits contains the integer sample delay (2's complement in the range of $\pm 8$ samples of |

|   | lelay). The fractional sample delay is used in sub-sample WIDAR delay compensation [3], and the                                                                                                                       |

|   | ractional as well as the integer delay is used in VLBI delay calculations on the correlator chip. The                                                                                                                 |

|   | 2 bits of delay information is transmitted LSB first                                                                                                                                                                  |

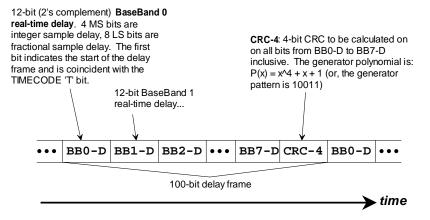

|   | 2 4-7 PHASEMOD format. A PHASEMOD frame can contain one or more linear phase models that                                                                                                                              |

|   | apply to one or more SDATA streams, defined by a baseband number and sub-band number pair                                                                                                                             |

|   | BB/SB). The models get loaded on the next occurrence of the TIMECODE 'T' bit (1PPS or                                                                                                                                 |

|   | 00PPS). Using this method, models can get updated as frequently as every 10 milliseconds, or as                                                                                                                       |

|   | nfrequently as desired. Note that since one PHASEMOD stream is generated for the entire station,                                                                                                                      |

|   | only some of the models will be applicable to a particular Recirculation Controller's SDATA inputs.                                                                                                                   |

|   |                                                                                                                                                                                                                       |

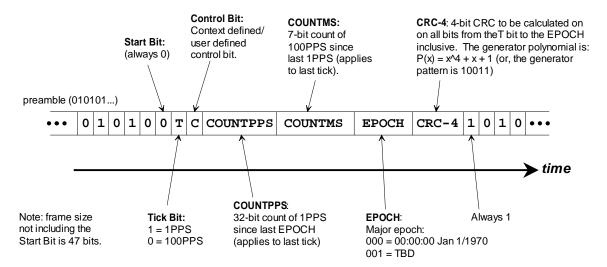

| _ | <b>4-8</b> TIMECODE format. The Control Bit tells receivers of SDATA whether or not to expect                                                                                                                         |

|   | embedded ID and CRC-4 data on this tick. If the Control Bit is 1, then the embedded data is present,                                                                                                                  |

|   | otherwise it is not. COUNTMS is not used by the Recirculation Controller to form the TIMESTAMP                                                                                                                        |

|   | hat is transmitted to the correlator chip, but it is used on the Station Board35                                                                                                                                      |

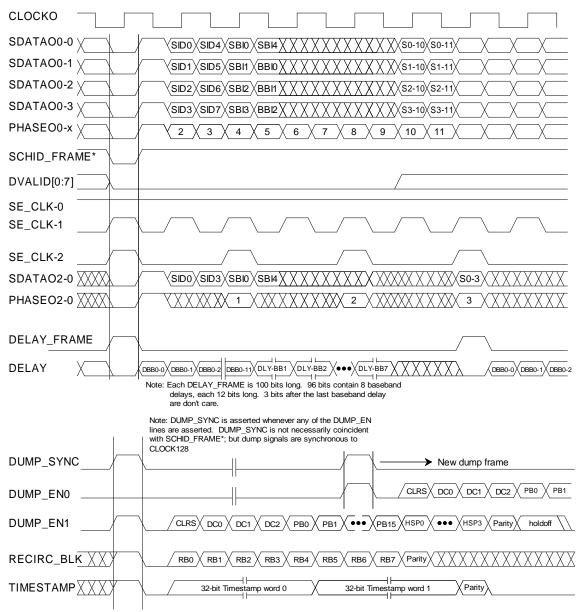

|   | <b>4-9</b> Functional timing diagram of signals transmitted by the Recirculation Controller to a row or                                                                                                               |

|   | column of correlator chips. Each signal contains a distinct 'eye' that allows simple real-time                                                                                                                        |

|   | monitoring of synchronization by the correlator chip even after a formal synchronization step has                                                                                                                     |

|   | been completed. If there is an error in the eye, the correlator chip can detect it and report the error via                                                                                                           |

|   | an associated data frame to the LTA Controller. SCHID_FRAME* and associated embedded                                                                                                                                  |

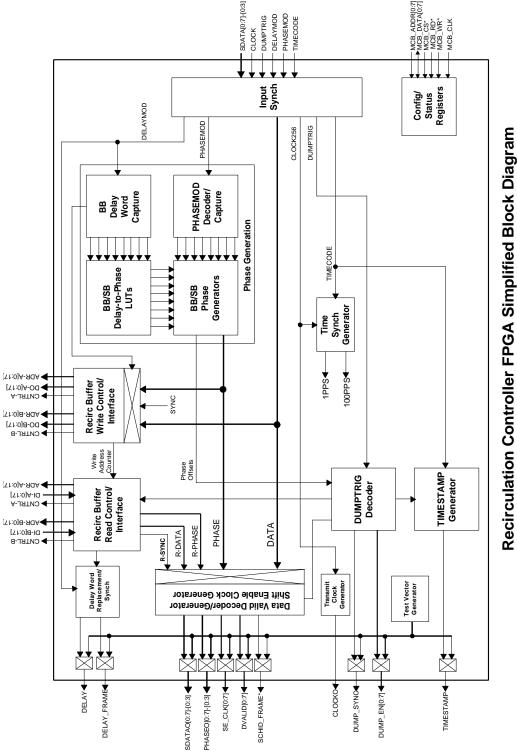

|   | information is only present when the Control Bit (i.e. the 'C' bit) of TIMECODE is present 37 see 4-10 Simplified block diagram of the Recirculation Controller. The device generates real-time 4-                    |

|   | pit phase that is transmitted to the correlator chip with the data. Phase is generated and carried with                                                                                                               |

|   | he data through the recirculation memory so there is no need for 'rewind control' of the phase                                                                                                                        |

|   | generators. A switch allows any output sampled data stream to be connected to any input or                                                                                                                            |

|   | ecirculation data stream. A Test Vector Generator is used to facilitate correlator chip timing and                                                                                                                    |

|   | ynchronization in an off-line procedure                                                                                                                                                                               |

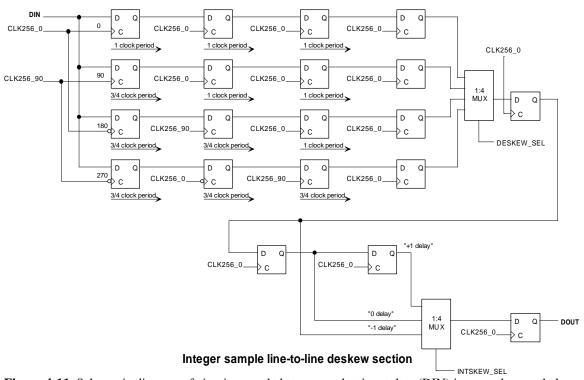

|   | <b>4-11</b> Schematic diagram of circuitry needed to ensure that input data (DIN) is properly sampled                                                                                                                 |

|   | and deskewed by the time it reaches the output (DOUT). The input data is sampled on 4 phases of a                                                                                                                     |

|   | 256 MHz clock and after several stages, it is all sampled on the same clock edge. The path with the                                                                                                                   |

| S | mallest error rate is selected with 'DESKEW_SEL'. Integer sample signal-to-signal skew is then                                                                                                                        |

|   | emoved by selecting the appropriately delayed signal with 'INTSKEW_SEL'. Additional logic is                                                                                                                          |

|   | equired for embedded signal detection and control of DESKEW_SEL and INTSKEW_SEL41                                                                                                                                     |

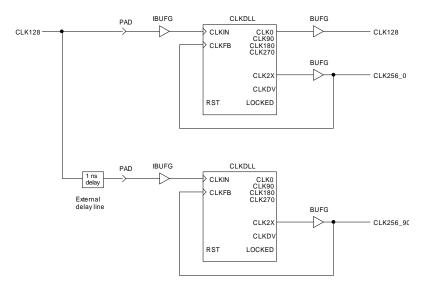

|   | <b>4-12</b> Xilinx Virtex-E DLL arrangement to produce desired internal 256 MHz clock phases. Two                                                                                                                     |

|   | DLLs are used along with a 1 nsec external delay line. A 128 MHz clock is also generated that can                                                                                                                     |

|   | be used for the recirculation memory and for transmission to the row or column of correlator chips. 41                                                                                                                |

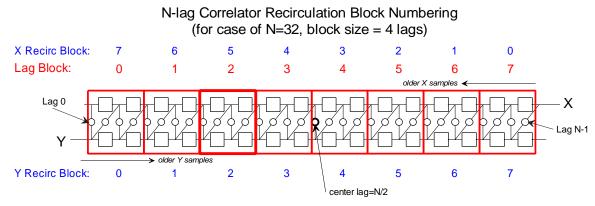

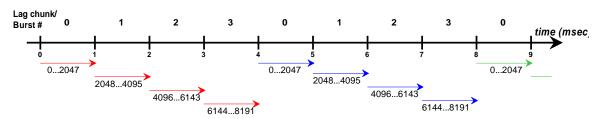

|   | <b>4-13</b> Simple 32-lag example with a lag block size of 4 lags. Here, we have a 4-lag correlator chip                                                                                                              |

|   | and we want to use recirculation to synthesize 32 lags. The 'Lag Block' indicates the chunk of the                                                                                                                    |

|   | ag chain that we want to synthesize on a given burst. The 'Y Recirc Block' indicates the number of                                                                                                                    |

|   | blocks of delay (equal to ½ the block lag size) that must be inserted in the Y-station data path for a                                                                                                                |

| - | particular Lag Block burst. The 'X Recirc Block' indicates the number of blocks of delay that must                                                                                                                    |

|   | be inserted in the X-station data path for the same Lag Block burst. For example, for Lag Block=2,                                                                                                                    |

|   | he Y Recirc Block is 2 (delay=4), and the X Recirc Block is 5 (delay=10). Data further down a shift                                                                                                                   |

|   | egister is older in time indicating that to 'insert delay' means to choose older samples in the ecirculation memory relative to the chosen zero relative delay point                                                  |

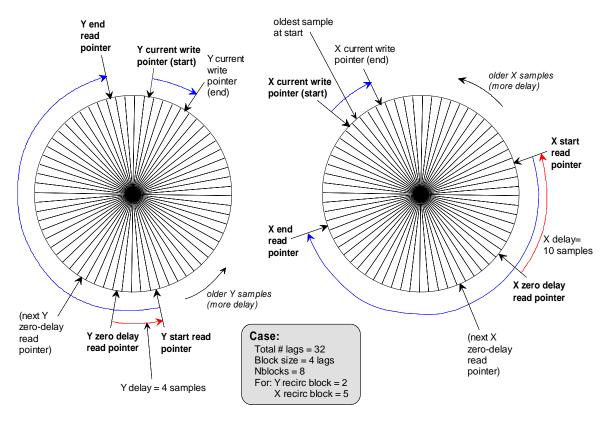

|   | <b>4-14</b> Example X and Y circular buffers for the simple recirculation example of Figure 4-13. The                                                                                                                 |

|   | absolute X and Y write pointers are not important as long as the zero-delay read pointers (which are                                                                                                                  |

|   | some function of the write pointers) point to samples that have a zero relative delay at some logical                                                                                                                 |

|   | nstant in time. The X and Y zero-delay read pointers are then offset in the direction of older samples                                                                                                                |

|   | more delay) to get the final start read pointers. Once the burst is complete, the X and Y write                                                                                                                       |

|   | pointers have advanced to new locations                                                                                                                                                                               |

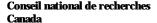

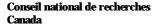

| <b>Figure 4-15</b> Circular buffer diagram of a real recirculation configuration to illustrate the time skew that   |

|---------------------------------------------------------------------------------------------------------------------|

| each recirculation burst experiences. The "ZD-n" pointer is the zero-delay read pointer for the n <sup>th</sup> lag |

| block. The "ST-n" pointer is the actual start read pointer for the n <sup>th</sup> lag block. Bold arrows indicate  |

| burst read pointer ranges for several bursts. The mean time stamp (MeanTS-n) is shown for each n <sup>th</sup>      |

| burst and the overall mean timestamp for the cross-power spectrum is "MeanTS". In this example,                     |

| we are recirculating by a factor of 16 with a 512k recirculation buffer and a correlator chip                       |

| integration time of 1 millisecond. The total integration time is 16 milliseconds, but the actual                    |

| "smear" time is 31 milliseconds                                                                                     |

| Figure 4-16 Diagram illustrating the relative real time of each burst of data with 16X recirculation and 1          |

| millisecond burst times. In this case, even though the integration time is only 16 milliseconds, the                |

| actual "smear time" of the data is 31 milliseconds                                                                  |

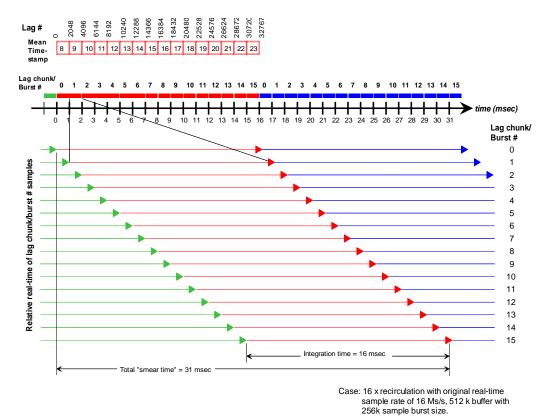

| Figure 4-17 Example illustrating the reduction in total smear time compared to the actual integration time          |

| when many (five in this case) bursts are integrated to yield one result46                                           |

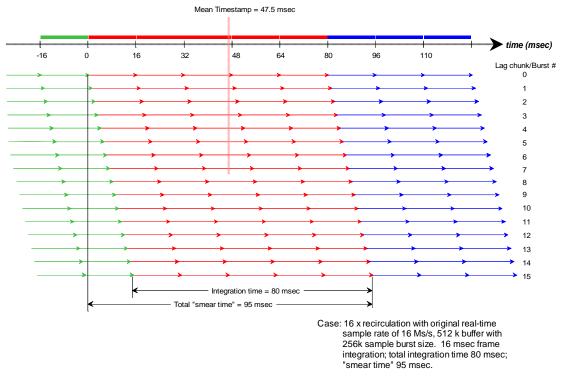

| <b>Figure 4-18</b> Time burst diagram of wide-band recirculation with a recirculation factor of 4. Here, 8192       |

| lags are synthesized with a 2048-lag correlator chip resulting in a factor of 2 penalty in sensitivity,             |

| but with a factor of 4 more spectral channels                                                                       |

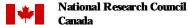

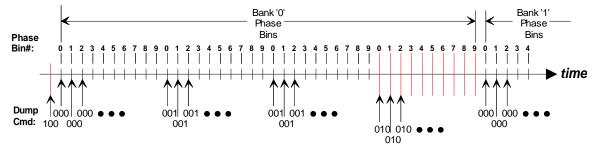

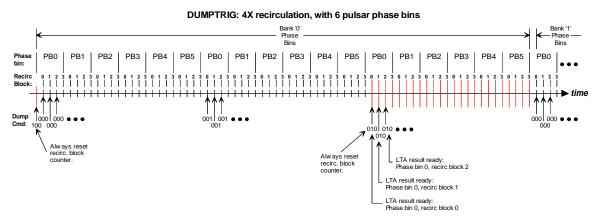

| Figure 4-19 DUMPTRIG timing diagram with 16X recirculation active. This diagram illustrates how                     |

| DUMPTRIG dump commands control the recirculation block counter, the phase bin number (every                         |

| dump requires a phase bin number), and tells the LTA controller what to do with the data49                          |

| Figure 4-20 DUMPTRIG commands and phase bins ('PBn') when recirculation is not active. The                          |

| sequence of commands is different than with recirculation. Note that the DUMPTRIG protocol                          |

| allows this sequence or the recirculation sequence to co-exist and use the same or different dump                   |

| epoch (as long as the epoch frequencies are harmonically related, that is)                                          |

| Figure 4-21 Example DUMPTRIG dump sequence with 10 pulsar phase bins. The dump command                              |

| sequence is similar to that of recirculation                                                                        |

| Figure 4-22 Example showing recirculation active when pulsar phase binning is active. In this example               |

| there is 4X recirculation and 6 pulsar phase bins                                                                   |

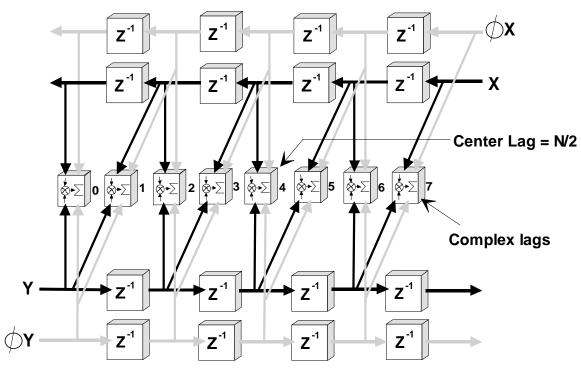

| Figure 4-23 Simplified block diagram of an example N=8-lag section. Lag numbering is a chosen                       |

| convention                                                                                                          |

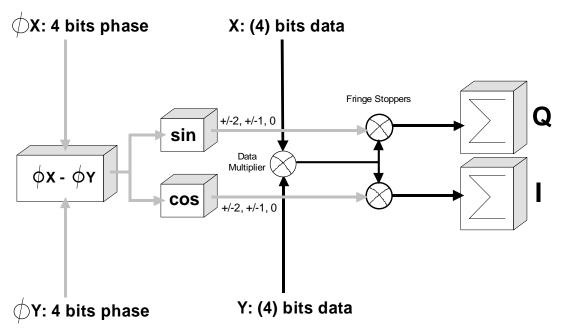

| Figure 4-24 Functional block diagram of one complex-lag in the correlator chip. In this design, only one            |

| X*Y data multiplier is required—important to reduce silicon and power dissipation with a 4-bit                      |

| multiplier. Five-level fringe stopping (complex phase rotation) is performed after data multiplication              |

| and can probably be done with relatively simple sign flips and bit shifts53                                         |

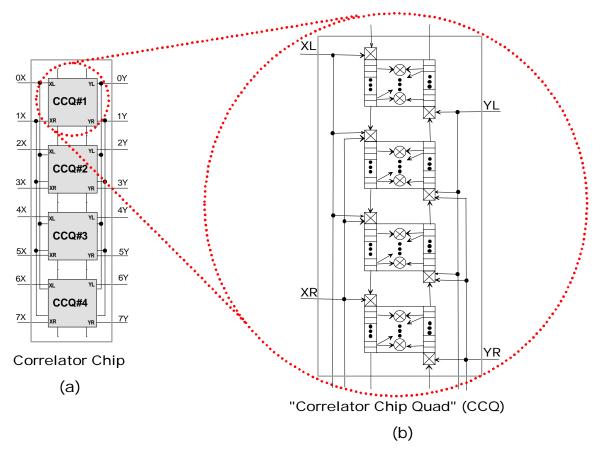

| Figure 4-25 Simplified correlator chip Correlator Chip Quad (CCQ) and lag arrangement. There are four               |

| CCQs (a) and each CCQ contains four, 128-lag cross-correlators (b). CCQ#1 is a master in that                       |

| every CCQ has access to its input data. Additionally, 128-lag correlator sections and CCQs can be                   |

| concatenated to yield combinations of lag correlators up to a single 2048-lag configuration 54                      |

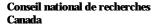

| Figure 4-26 Correlator chip black-box diagram. There are X and Y inputs, an LTA controller interface                |

| and an MCB interface. The 'CLOCK' input is the 128 MHz clock that can come from either the X or                     |

| Y Recirculation Controller since the safe assumption is made that X and Y input signals are skewed                  |

| in time relative to the clock and each other                                                                        |

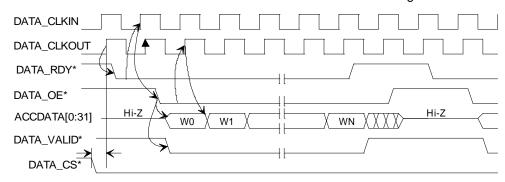

| Figure 4-27 Correlator chip LTA controller interface functional timing. Once enabled by the LTA                     |

| Controller and if data is ready, the correlator chip transmits data to the LTA Controller. Once                     |

| transmission is complete, the particular 128-lag section buffer registers are cleared to capture more               |

| data. Not shown in this timing diagram is FRAME_ABORT* that aborts transmission of the current                      |

| frame and clears the lag section buffer registers                                                                   |

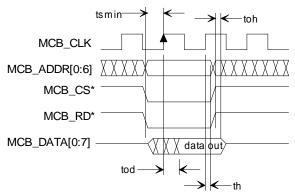

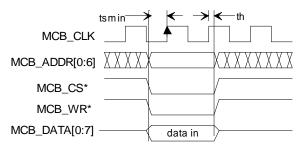

| Figure 4-28 Correlator chip MCB interface READ and WRITE cycle functional timing diagrams. Seven                    |

| address bits are shown, but the actual number required requires further definition. MCB_CLK has a                   |

| nominal maximum frequency of 128 MHz—although it would normally be much lower than that 57                          |

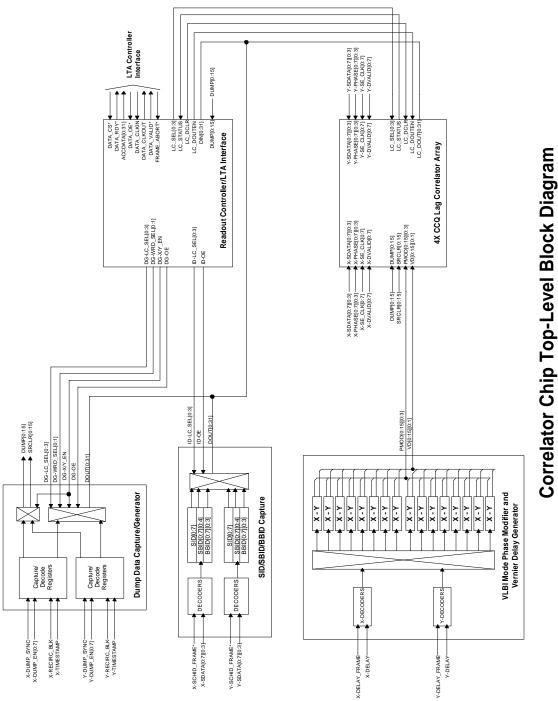

| Figure 4-29 Correlator chip top-level block diagram. This diagram contains straw-man concepts for all               |

| functional blocks and interconnect signals required for correlator chip functions. Not shown is the                 |

| logic required for synchronization of X and Y input data (test vector receivers, de-skew controllers                |

| etc.)                                                                                                               |

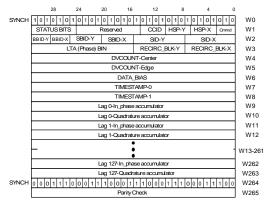

| Figure 4-30 Correlator chip output data frame. Each frame contains header information and lag data from             |

| one of the 16, 128-lag lag cells. Data valid counts are provided that are at the center lag (lag N/2) and           |

| at an edge lag (lag 0). By providing counts at these locations, a center lag and an edge lag data valid             |

| count are always available even when multiple lag cells are concatenated to form a longer lag chain.                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Two data valid counts can help to mitigate the systematic effects of data valid blanking that occurs at                                                                                           |  |

| the same time in both X and Y stations. Note that even if multiple 128-lag cells are concatenated,                                                                                                |  |

| each output data frame only ever contains data from one lag cell                                                                                                                                  |  |

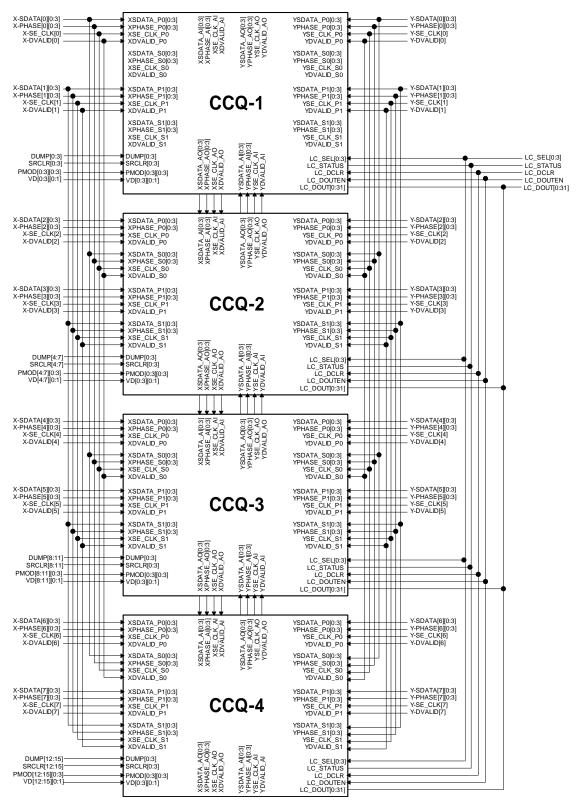

| Figure 4-31 Detailed block diagram of the array of four CCQs. CCQ-1 is the master and CCQs 2-4 are                                                                                                |  |

| the slaves in that they have access to the master's input data. Data flows between adjacent CCQs so                                                                                               |  |

| that chaining of CCQs can occur                                                                                                                                                                   |  |

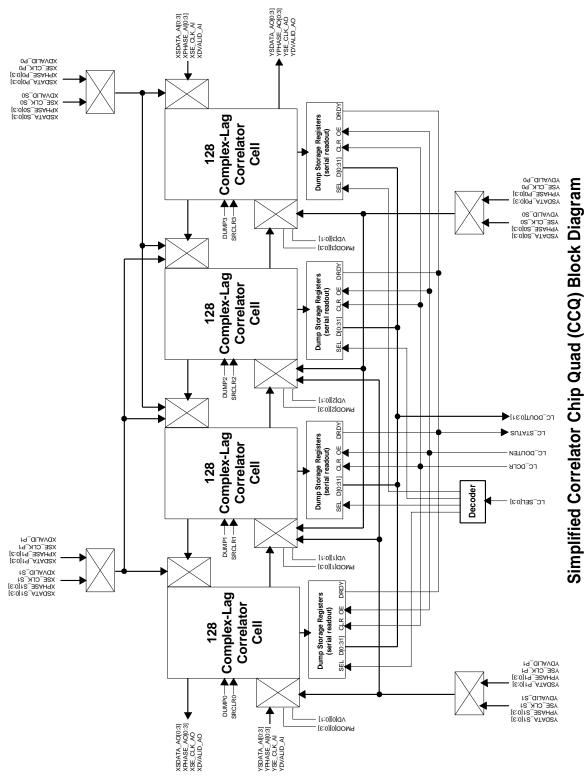

| Figure 4-32 Simplified block diagram of one correlator chip CCQ. There are four, 128 complex-lag                                                                                                  |  |

| 'cells'—each cell has the lag architecture as shown in <b>Figure 4-23</b> . Switches in front of the X and Y                                                                                      |  |

| inputs of each cell allow the cell to select new data, master data, or data from an adjacent cell 63                                                                                              |  |

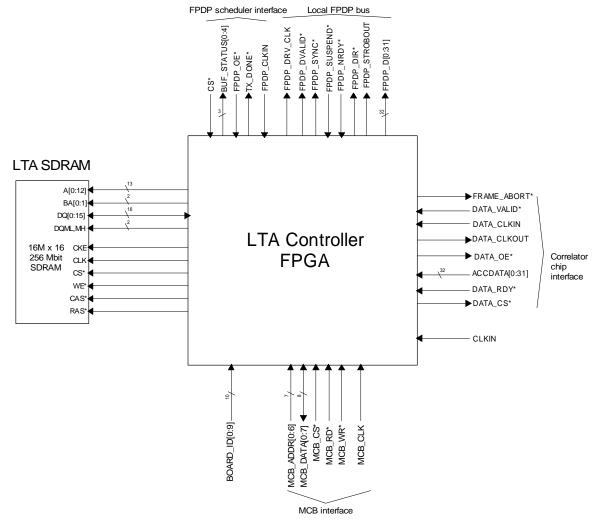

| Figure 4-33 Black box diagram of the LTA Controller FPGA. Data enters the device via the correlator                                                                                               |  |

| chip interface, is saved in the SDRAM, and when ready, exits the chip via the local FPDP bus. Transmission by a particular LTA Controller on the local FPDP bus is determined by signaling on the |  |

| FPDP scheduler interface                                                                                                                                                                          |  |

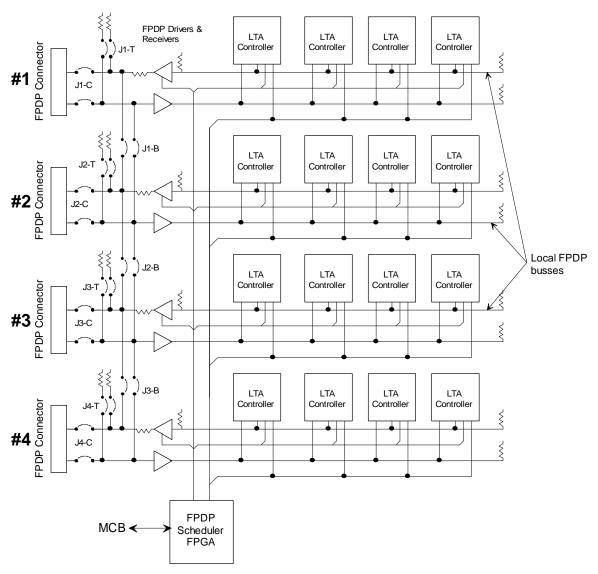

| Figure 4-34 Simplified LTA Controller/FPDP interface diagram. Only 16 LTA Controllers are shown but                                                                                               |  |

| in reality there will be 64. There are 4 local FPDP busses that can terminate on anywhere from 1 to 4                                                                                             |  |

| external FPDP interfaces depending on jumper settings. Each local bus has its own FPDP drivers. <b>67</b>                                                                                         |  |

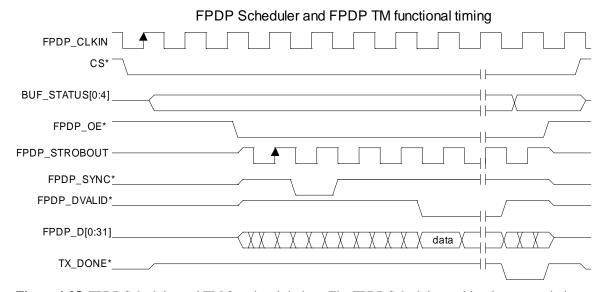

| Figure 4-35 FPDP Scheduler and TM functional timing. The FPDP Scheduler enables data transmission                                                                                                 |  |

| from a particular LTA Controller by asserting the FPDP_OE* line. The LTA Controller indicates it                                                                                                  |  |

| has finished transmitting a frame by asserting the TX_DONE* line for one clock cycle                                                                                                              |  |

| Figure 4-36 LTA dump data frame transmitted from the LTA Controller. This is data read from the LTA                                                                                               |  |

| RAM after one or more dumps from the correlator chip have been integrated. The DATA_BIN# is                                                                                                       |  |

| the actual physical bin (of two banks of 1000 each) that the data comes from. This can be different                                                                                               |  |

| than the 'phase bin' specified by DUMPTRIG if recirculation is active. The phase bin number is a                                                                                                  |  |

| simple post-correlation calculation involving DATA_BIN# and the number of recirculation blocks                                                                                                    |  |

| active. Note that the integrated DATA_BIAS is not present in the frame because this would quickly                                                                                                 |  |

| overflow the 32-bit limit                                                                                                                                                                         |  |

| Figure 4-37 Speed dump data frame transmitted from the LTA Controller. This is data that has by-passed                                                                                            |  |

| the LTA RAM and essentially comes straight from the correlator chip. This frame is very similar to                                                                                                |  |

| the correlator chip output data frame of Figure 4-30. Note that the LTA Controller includes the                                                                                                   |  |

| DATA_BIAS in this frame even though it has already been removed from the data71                                                                                                                   |  |

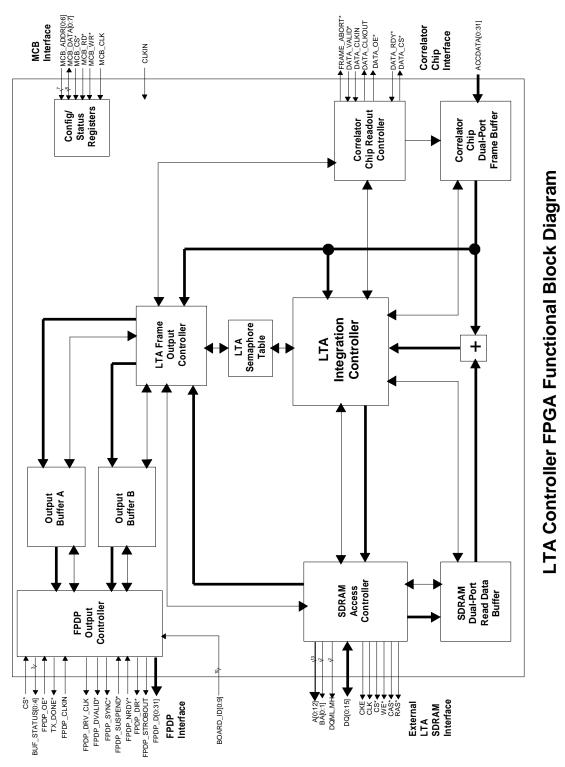

| Figure 4-38 LTA Controller functional block diagram. Data enters into a frame buffer from the correlator                                                                                          |  |

| chip. If required, at the same time, data is read from SDRAM into the SDRAM read buffer. These                                                                                                    |  |

| data are integrated and written back to SDRAM. When an SDRAM data bin is ready for output, an                                                                                                     |  |

| associated semaphore is set in the LTA Semaphore Table. The frame output controller looks at the                                                                                                  |  |

| semaphore table for ready data and then transfers ready data from the SDRAM into output buffer A                                                                                                  |  |

| or B, where it is eventually transmitted onto the FPDP interface                                                                                                                                  |  |

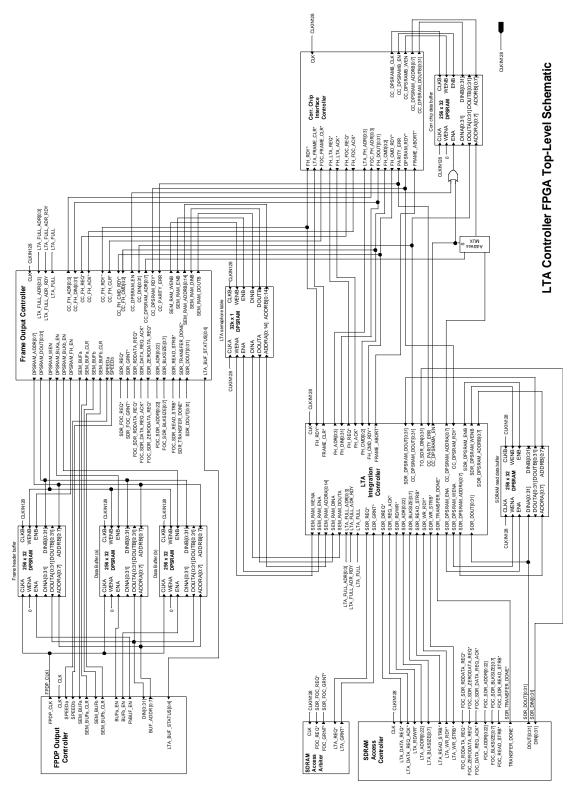

| Figure 4-39 LTA Controller paper design top-level schematic. There are 31 schematic sheets in the                                                                                                 |  |

| design and the design entry time was 6 person-weeks. This design should comfortably fit in a \$20                                                                                                 |  |

| FPGA (XCV100E-6FG256C)                                                                                                                                                                            |  |

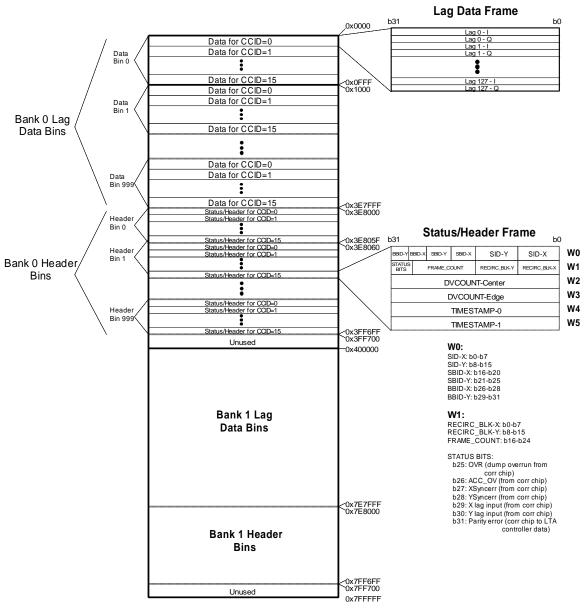

| Figure 4-40 LTA SDRAM memory map. There are two banks of (exactly) 1000 phase bins (or more                                                                                                       |  |

| correctly, data bins) each. A lag data frame and a status/header data frame and their contents are                                                                                                |  |

| defined. A CCID is the same as a correlator chip 'lag cell'—a single 128 complex-lag correlator block. Note that the CCID is not stored in the LTA memory since the CCID is a function of the LTA |  |

| memory address and therefore does not have to be stored                                                                                                                                           |  |

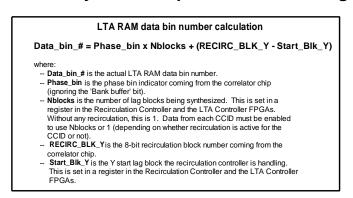

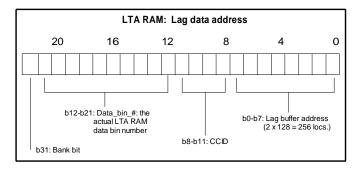

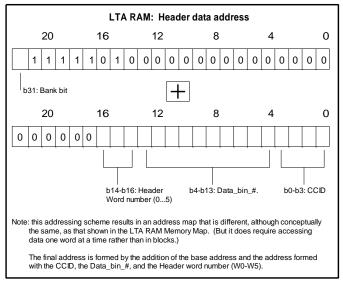

| Figure 4-41 Specific LTA memory addressing information. The top box is the equation used to calculate                                                                                             |  |

| the actual data bin number that a particular phase bin maps into when recirculation is active. The                                                                                                |  |

| middle box is the lag data address breakdown. The bottom box is the header data address breakdown.                                                                                                |  |

| Note that, for logic simplicity, the header data is not contiguous in memory as conceptually shown in                                                                                             |  |

| the LTA SDRAM Memory Map. However, the memory can be thought of as being contiguous as                                                                                                            |  |

| long as burst accesses are not performed                                                                                                                                                          |  |

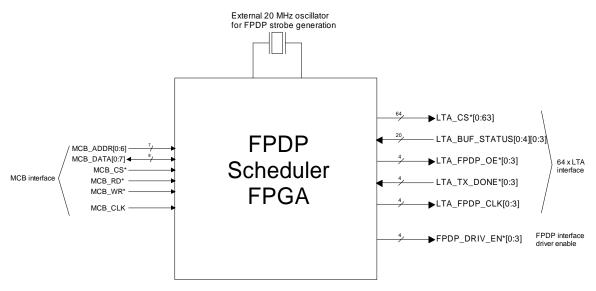

| Figure 4-42 FPDP Scheduler FPGA black-box diagram. This device queries each LTA Controller to                                                                                                     |  |

| determine its priority for data transmission on the FPDP. When the highest-priority LTA Controller                                                                                                |  |

| has been identified, it and its associated FPDP interface drivers are enabled                                                                                                                     |  |

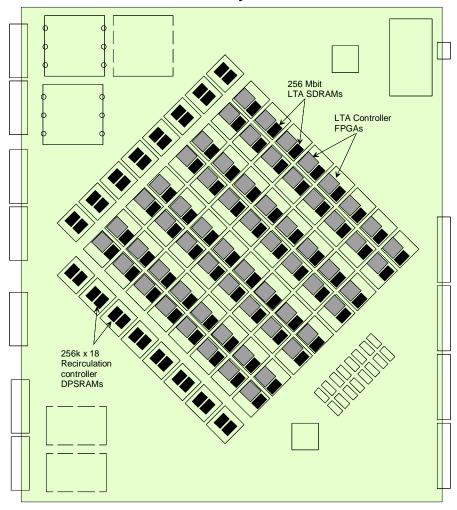

| Figure 4-43 Baseline plan for the physical layout of the Baseline Board. The 8x8 correlator chip array and                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| associated circuitry is rotated by 45° for better X and Y signal delay matching than would be obtained without the rotation                                                                                      |  |  |

| Figure 4-44 Baseline Board rear-side physical layout. Behind each correlator chip is its associated LTA                                                                                                          |  |  |

| Controller and SDRAM. Behind each Recirculation Controller are its associated DPSRAMs                                                                                                                            |  |  |

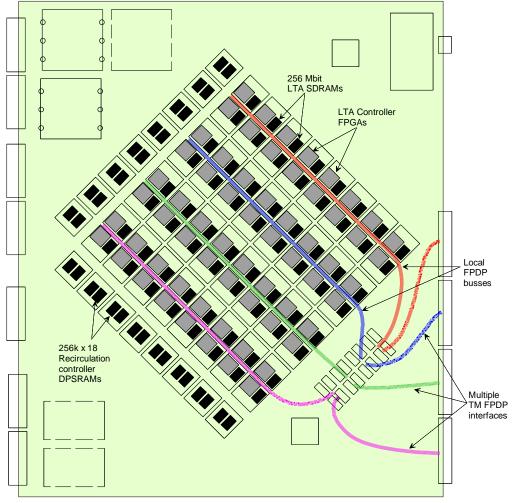

| Figure 4-45 Baseline Board high speed data routing paths. The paths in red are X-station data and the                                                                                                            |  |  |

| paths in blue are Y-station data. This orientation has better delay-path matching than a vertical                                                                                                                |  |  |

| orientation of the correlator chip array, however there is still path mismatch. The worst case                                                                                                                   |  |  |

| mismatch is shown to a correlator chip (in green). The mismatch is the difference between the                                                                                                                    |  |  |

| hypotenuse and the side of the 45-45-90 triangle (yellow) shown                                                                                                                                                  |  |  |

| <b>Figure 4-46</b> Baseline Board high-speed data routing for better X/Y delay-path matching. The longer the                                                                                                     |  |  |

| data path is from the connectors to the Recirculation Controllers, the more additional routing delay is                                                                                                          |  |  |

| added. This routing ensures that X and Y data arrives at the correlator chips at about the same time—                                                                                                            |  |  |

| reducing the delay-path mismatch circuitry requirements in the correlator chip                                                                                                                                   |  |  |

| <b>Figure 4-47</b> Local FPDP bus routing with one active external FPDP transmit interface. The FPDP                                                                                                             |  |  |

| Scheduler enables only one correlator chip and one set of FPDP drivers at a time. With this                                                                                                                      |  |  |

| arrangement and a 100 Mbytes/sec FPDP interface, all lags from all correlator chips can be dumped                                                                                                                |  |  |

| about every 11 milliseconds. This should be more than adequate for most applications                                                                                                                             |  |  |

| <b>Figure 4-48</b> Local and external FPDP data routing with all four FPDP interfaces installed and enabled. With 400 Mbyte/sec FPDP-II capability, all lags from all correlator chips could be dumped every 700 |  |  |

| μsec                                                                                                                                                                                                             |  |  |

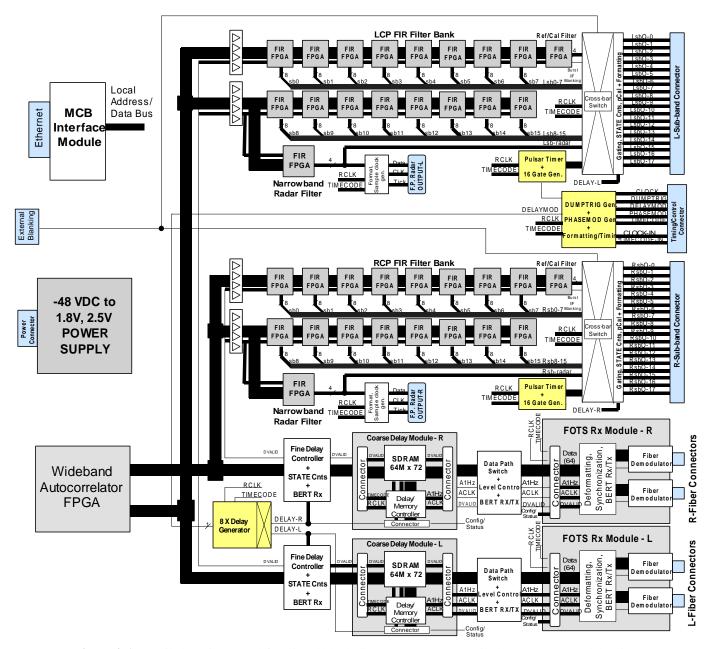

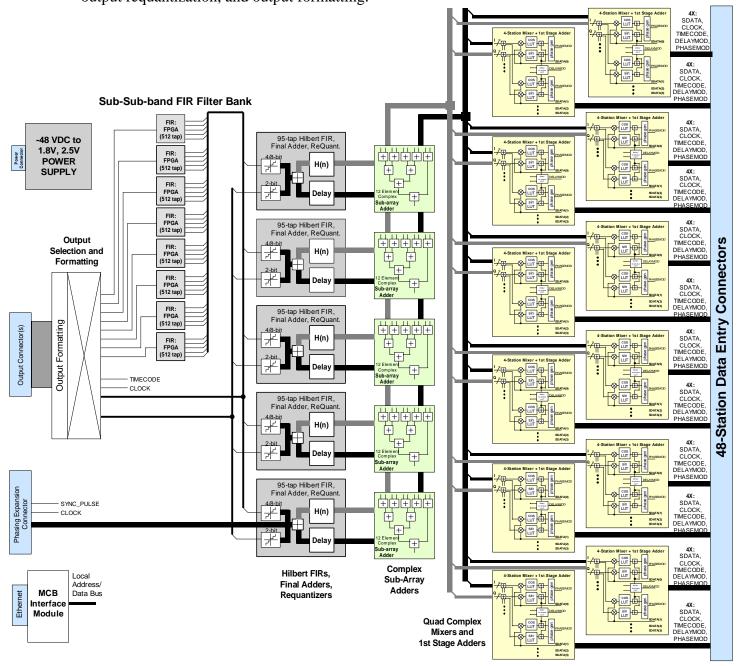

| Figure 5-1 Phasing Board block diagram. Up to 5 sub-arrays from up to 48 stations can be handled. The                                                                                                            |  |  |

| output section allows phased sub-bands to be split into "sub-sub-bands" using digital FIR filters in                                                                                                             |  |  |

| FPGAs, and an output switch selects the desired data. Simultaneous 2 and 4/8-bit re-quantization is                                                                                                              |  |  |

| possible, and a non-requantized output connector is provided for expansion beyond 48 stations 84                                                                                                                 |  |  |

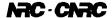

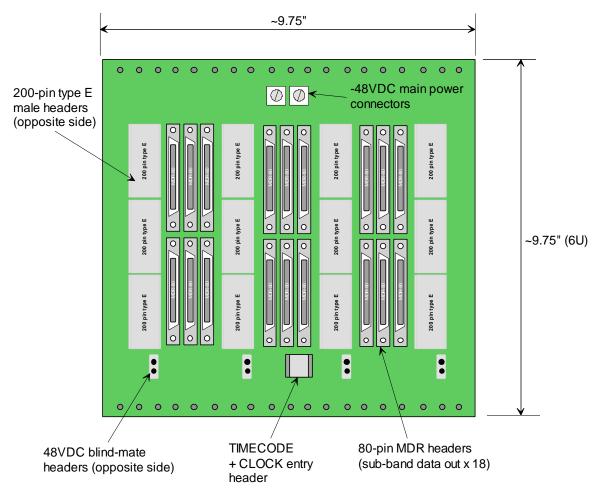

| Figure 6-1 Preliminary layout of the Sub-band Distributor Backplane. Four Station Boards plug into it,                                                                                                           |  |  |

| and each MDR-80 connector contains data from one sub-band of basebands from all Station Boards.                                                                                                                  |  |  |

| Station Boards are spaced apart so that each one has 3 full (VME) slots to itself                                                                                                                                |  |  |

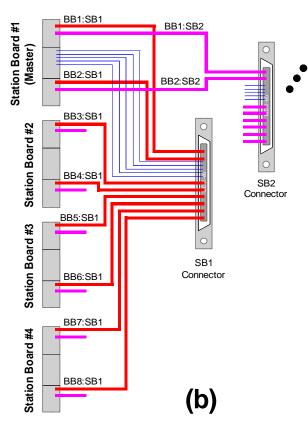

| Figure 6-2 Sub-band Distributor Backplane data routing. In (a), data routing for the physical board is                                                                                                           |  |  |

| shown for one connector. The thick red lines are sub-band data, and the thin blue lines are control                                                                                                              |  |  |

| signals (CLOCK, TIMECODE, DUMPTRIG, DELAYMOD, PHASEMOD). (b) is a pseudo-                                                                                                                                        |  |  |

| schematic representation of the connections on the board                                                                                                                                                         |  |  |

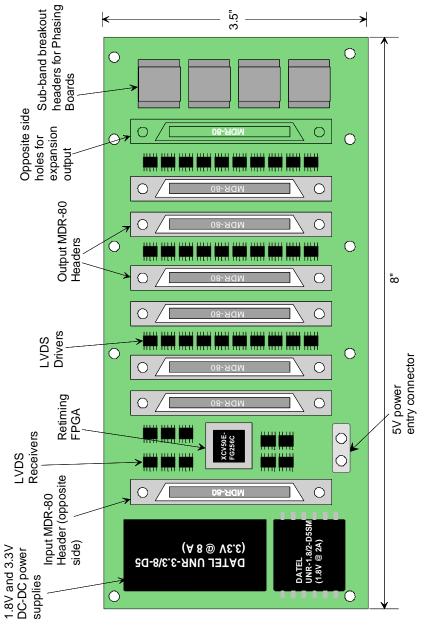

| <b>Figure 6-3</b> MDR-80 header/socket pin locations. Source: 3M data sheet, P/N 10280-6212VC91 <b>Figure 6-4</b> Station Data Fanout Board physical layout. The sub-band cable input is fanned-out by a factor  |  |  |

| of 6 with an additional output for routing to other racks. Also, breakout for cables going to Phasing                                                                                                            |  |  |

| Boards is provided (shown here with a sub-band pair per breakout). MDR-80 pinouts are according                                                                                                                  |  |  |

| to Figure 6-3 and Table 6-1                                                                                                                                                                                      |  |  |

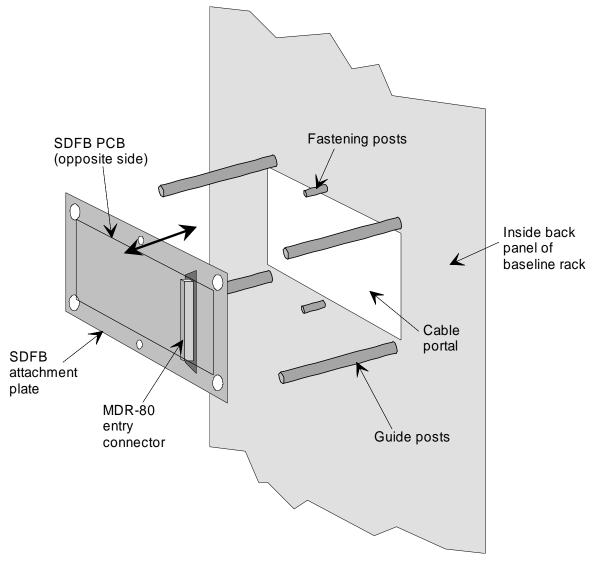

| Figure 6-5 Straw-man concept for fastening the Station Data Fanout Board (SDFB) to the inside back                                                                                                               |  |  |

| panel of the baseline rack. It must be possible to hot-swap the SDFB without shorting any signals or                                                                                                             |  |  |

| power. The guide posts allow the SDFB assembly (includes the PCB and an attachment plate) to be                                                                                                                  |  |  |

| safely extracted from the panel so that the existing cabling that feeds through the "cable portal" and                                                                                                           |  |  |

| connects to the SDFB PCB can be removed. The fastening posts protrude through the attachment                                                                                                                     |  |  |

| plate and are used to fasten the SDFB assembly with wing-nuts. Not shown is a power switch                                                                                                                       |  |  |

| protruding through the SDFB attachment plate to remove +5V power from the PCB                                                                                                                                    |  |  |

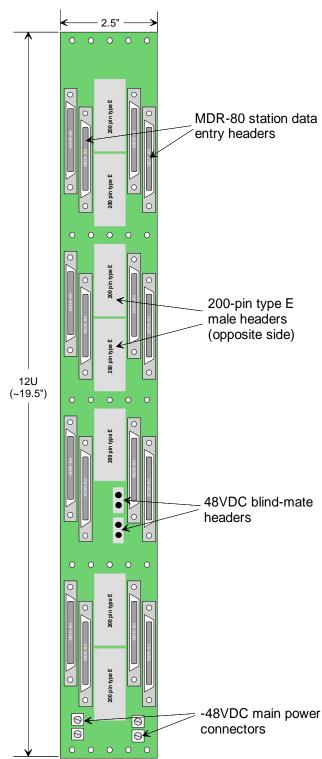

| <b>Figure 6-6</b> Baseline Entry Backplane physical layout. This backplane routes signals on the 16 (8 'X'; 8                                                                                                    |  |  |

| 'Y') input MDR-80 connectors to connectors that blind-mate with the front-entry Baseline Board.                                                                                                                  |  |  |

| The MDR-80 connectors are staggered to prevent "pile-up" of cable that is thicker than the                                                                                                                       |  |  |

| connector                                                                                                                                                                                                        |  |  |

| sub-band pairs                                                                                                                                                                                                   |  |  |

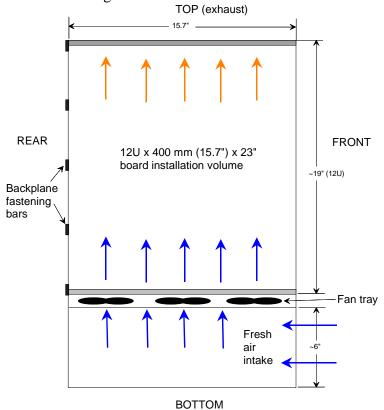

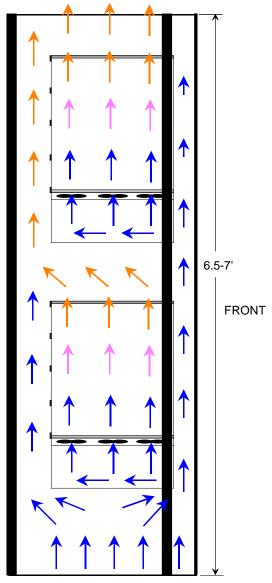

| Figure 7-1 Profile of a straw-man design for the sub-rack. Each sub-rack has its own fresh (cool) air                                                                                                            |  |  |

| supply. The fans in the fan tray can fail and thus must be able to be hot-swapped                                                                                                                                |  |  |

| Figure 7-2 Profile of 7' rack with two 12U sub-racks. Approximate airflow vectors are shown with                                                                                                                 |  |  |

| arrows                                                                                                                                                                                                           |  |  |

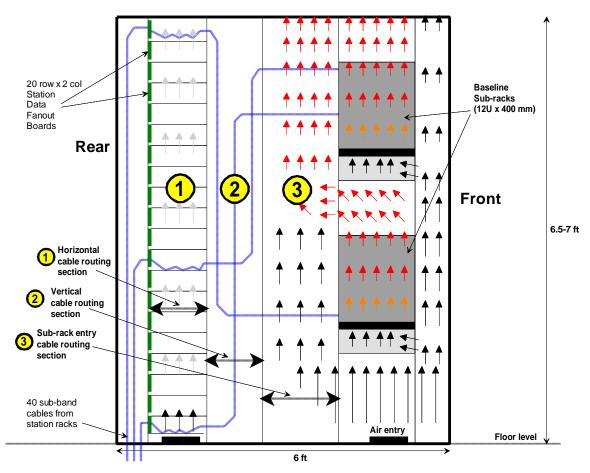

| <b>Figure 7-3</b> Baseline rack profile showing 2 baseline sub-racks, approximate airflow vectors, Station Data                                                                                                  |  |  |

| Fanout Boards, and a straw-man cable routing plan. Cables from station racks (Sub-band Distributor                                                                                                               |  |  |

Canada

| Backplanes) enter through the floor at the back and plug into Station Data Fanout Boards. Cable                          |

|--------------------------------------------------------------------------------------------------------------------------|

| from the Station Data Fanout Boards (up to 256 cables, each one 3 m long) is routed in three sections                    |

| as shown. In the first section, cable is routed horizontal-only (into the plane of the figure) until it                  |

| reaches the correct location. In the second section, cable is routed vertical-only until it reaches the                  |

| right vertical location. In the third section, cable is routed horizontal-only directly to its plug-in poin              |

| on the Baseline Entry Backplane. Sections are separated by "grids" that constrain the cable paths. 10                    |

| Figure 7-4 Routing of DC-DC converter monitor and control lines for each rack. Each rack has a single                    |

| cable used for power supply monitor and control                                                                          |

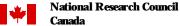

| Figure 7-5 Possible 40-station correlator floor plan. The station racks are in the center of all of the racks            |

| since cable from each station rack goes to every baseline rack, each cable must be the same length,                      |

| and it is desirable to minimize the cable lengths. The floor plan has dimensions of 35 x 43 ft, and                      |

| there is enough room for additional racks of equipment. Data output processing computers could be                        |

| mounted in racks or shelves beside each baseline rack so as not to interfere with access to baseline                     |

| rack cabling. The location of the TIMECODE Generator Box is not yet defined, but it can probably                         |

| be located in one of the central station racks                                                                           |

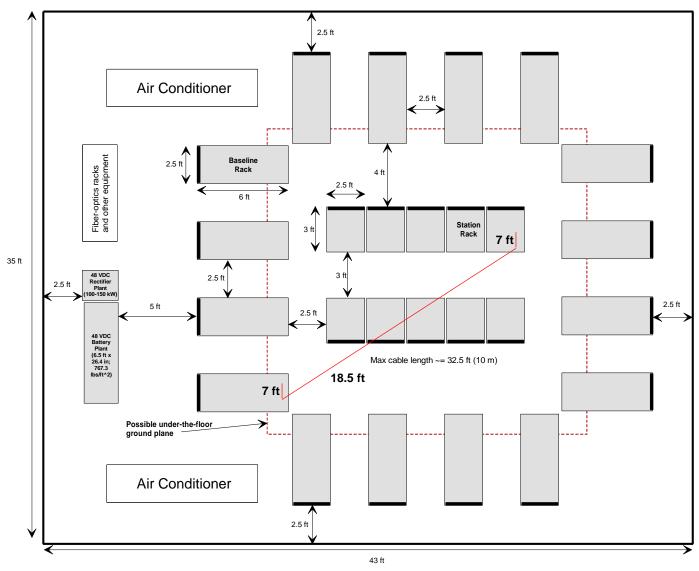

| <b>Figure 7-6</b> Possible <b>48-station</b> correlator floor plan. In this arrangement, 3 baseline racks contain all of |

| the boards for 2 sub-band correlators and so there are a total of $1.5 \times 16 = 24$ baseline racks. The               |

| station racks are in the center of all of the racks since cable from each station rack goes to every                     |

| baseline rack, each cable must be the same length, and it is desirable to minimize the cable lengths.                    |

| The floor plan has dimensions of 45 x 50 ft, and there is enough room for additional racks of                            |

| equipment. Data output processing computers could be mounted in racks or shelves beside each                             |

| baseline rack so as not to interfere with access to baseline rack cabling. The location of the                           |

| TIMECODE Generator Box is not yet defined, but it can probably be rack-mounted in one of the                             |

| central station racks                                                                                                    |

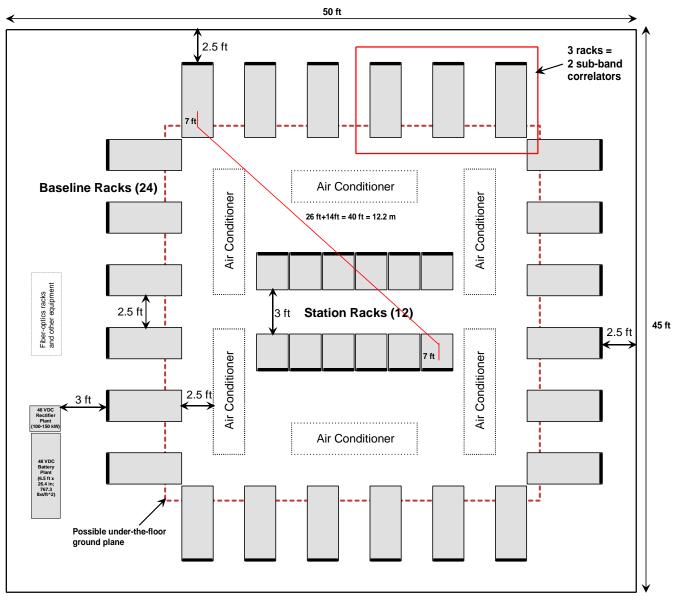

| Figure 7-7 Artist's rendering of the 48-station correlator installation                                                  |

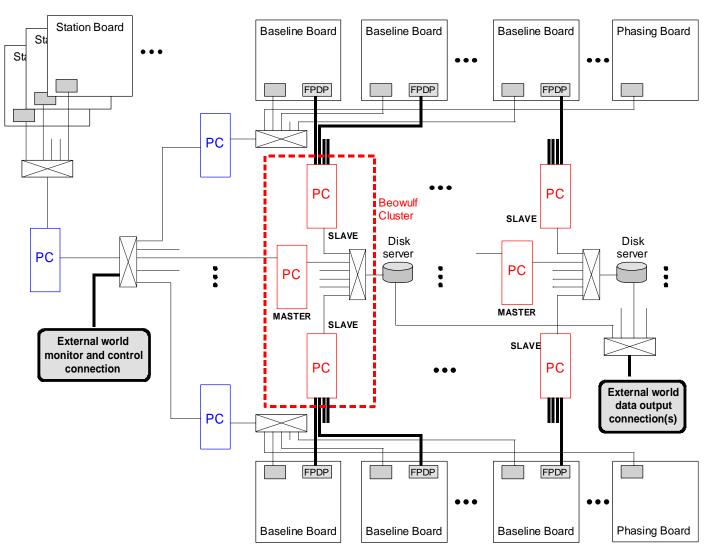

| Figure 7-8 Straw-man correlator computing environment. COTS PC boxes are control computers and                           |

| data processing computers. The data processing computers are arranged in Beowulf clusters so that                        |

| each cluster gets data from Baseline Boards that process the same baselines. With this configuration                     |

| there is no need for inter-cluster communication that could produce unacceptable bottlenecks in some                     |

| correlator configurations. Performance is increased by increasing the <i>number of clusters</i> (i.e. each               |

| PC crunches data from fewer Baseline Boards), not the cluster size. The master PC in each cluster is                     |

| used to obtain configuration information, not available on the FPDP interface, that is necessary for                     |

| creating FITS file frogments                                                                                             |

## 1 Executive Summary of Correlator Capabilities

This section provides an overview of the capabilities of the correlator described in this document. Some of these capabilities exist to meet EVLA science and system requirements, and others evolved from the chosen signal processing and architecture.

- 16 GHz of bandwidth per antenna arranged as eight 2 GHz basebands (or four pairs). Bandwidth can be traded-off for number of antennas without correlator modification. Inputs support flexible allocation of basebands and baseband widths.

- Each 2 GHz baseband input can be on a different delay center on the sky for flexible multi-beaming. Different baseband inputs could process the same data (with a frontend switch) with a completely different delay center.

- 16,384 spectral channels per baseline at the widest bandwidths. Up to 256k spectral channels per *cross-correlation* on 2 basebands using "recirculation". "Wideband recirculation" provides more spectral channels at wide bandwidths with sensitivity losses.

- High performance data output capability. The nominal 40-station configuration could produce ~3 Gvis/sec. The extreme 40-station configuration could produce ~12 Gvis/sec. However, the output data rate will largely be determined by back-end processing capability, and data volume handling limits.

- ≤4 or 8-bit sampling and/or correlation for high spectral dynamic range and spectral purity.

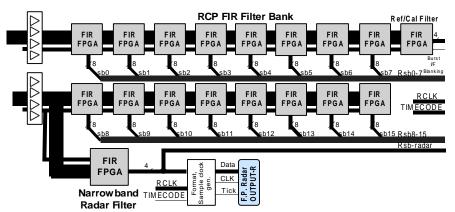

- 144 digital filters per station generate sub-bands for flexible deployment of spectral resources and efficient wideband correlation. Each sub-band can be on a different delay center on the sky, within a maximum offset of about 0.25° from the baseband delay center (e.g. for a 2000 km baseline). "Radar-mode" sub-bands can be as narrow as 30 kHz.

- Pulsar processing: 2 banks of 1000 time bins/sub-band/baseline (up to 65k bins with back-end S/W binning); bin width as narrow as 15 μsec; independent timer for each baseband; independent gate for each sub-band.

- LO shifting for anti-aliasing and RFI robustness. Decorrelation of sampler-generated self-interference, strong narrowband harmonics, and many intermodulation products. Decorrelation of interleaved sampler artifacts.

- Real-time or tape-based VLBI capable.

- Reconfiguration/expansion capable.

- Simultaneous interferometer and phased-VLA operation. Delivered with a 1 GHz phased bandwidth, expandable to a full 16 GHz without re-design or replacement of existing hardware or cabling.

- Many interferometer and phased-array sub-arraying possibilities.

- All-digital sub-sample delay tracking to  $\pm 1/32^{\text{nd}}$  of a sample.

#### 2 System Overview

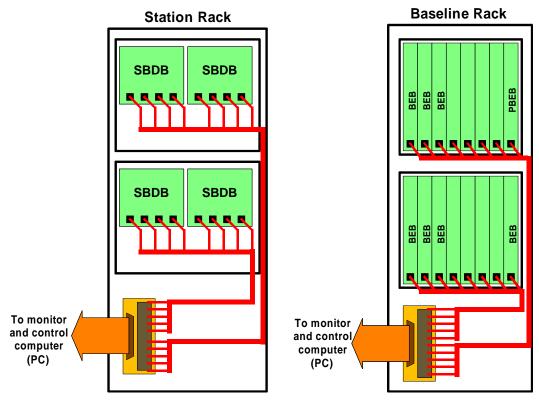

The EVLA correlator hardware components consist of three main digital printed circuit boards, a few small backplanes and interconnect modules, and high-performance cabling. Using these few components as building blocks it is possible to construct a correlator of virtually any size and configuration. A simplified correlator module connectivity diagram is shown in Figure 2-1. All modules in this diagram will be described in detail in following sections. All fiber-optics components and cards are not within the development scope of the correlator and will be developed by NRAO.

**Figure 2-1** Simplified correlator module connectivity diagram. The three main boards are the Station Board, the Baseline Board, and the Phasing Board. Data and signal flows are as indicated by the red arrows.

Data from the antennas arrives via fiber-optic links where it is wavelength demodulated before being presented to mezzanine cards on the Station Boards. On these cards, the fiber-optic signal is demodulated into electrical signals for use by Station Board electronics. Each "station input" in the correlator consists of four Station Boards: one "master" input and three "slave" inputs. The master Station Board is the one that

Canada

generates all of the timing, model, and control signals for downstream processing, whereas the slave Station Boards are only used for data generation. Aside from these differences, each of the four Station Boards' functions is the same. Each Station Board handles two, 2 GHz sampled basebands—also referred to as a baseband pair. The Station Board "Delay" mezzanine card compensates for wavefront geometric delay as well as delay through the fiber-optic system. Data then goes to the sub-band FIR filter banks, the output of which is 16 (with provision for 18) sampled data streams no longer in demultiplexed parallel form as it was going into the filters. This data goes through crossbar switches before going to the Sub-band Distributor Backplane, which passively rearranges the data so that there are 16 (with provision for 18) sub-band cable outputs. Each sub-band cable output contains data, timing, model, and synchronization information for one sub-band from all 8 basebands from one station. All real-time information required for the down-stream Baseline Boards (recirculation, phase-binning, dumping, phase models, delay models) is generated on the Station Boards and flows with the data on each sub-band cable. Data gets distributed and fanned-out to all of the Baseline Boards and the Phasing Boards via Station Data Fanout Boards and data routing backplanes.

On the Baseline Board, there are 8 'X-station' and 8 'Y-station' inputs—each input being data from one sub-band cable from one station. The input data is resynchronized and formatted for transmission to a row or column of correlator chips by the 8 'X' and 8 'Y' Recirculation Controllers. The 8x8 matrix of correlator chips correlate data and respond to commands coming from the Recirculation Controllers. After integration, and on command from Recirculation Controllers, the data is read out of the correlator chip by its own dedicated LTA (Long-Term Accumulator) Controller and saved in LTA RAM. Although having one LTA Controller for each correlator chip seems extreme, it offers significant performance advantages and is cost-effective since a relatively small (and inexpensive) FPGA can be used. When enabled by an on-board FPDP (Front Panel Data Port) scheduler, LTA data is transmitted via FPDP to an external computer (PC) for further processing. The data on the Baseline Board is not handled by a microprocessor so there are virtually no bottlenecks to data flow off the board.

On the Phasing Board, data for one sub-band<sup>1</sup> from all antennas enters via the Phasing Board Entry Backplane. This is the same data that goes to the Baseline Boards only it is rearranged so that only one sampled data stream (one sub-band of one baseband) and associated timing/synchronization information is contained on one cable. Thus, each Phasing Board sums antennas for one sub-band of one baseband. Data is summed in two stages to keep on-board data path widths within device capabilities. In the first-stage, data from antennas are summed in groups of 4. Each antenna's data is complex multiplied before complex addition to remove the Doppler shift and the frequency shift required by the WIDAR technique. There are 5, second-stage adders—each one being the output of one sub-array. After second-stage addition, the complex data is combined using the Hilbert transform FIR, the second part of the digital single-sideband mixer. Details and test results are found in [9]. The final summed output is available in normal

<sup>&</sup>lt;sup>1</sup> Although the goal is to phase two sub-bands, or a sub-band pair on every Phasing Board. This will be done if determined to be practical at the detailed design stage.

sub-band "wide" mode, or it can be filtered with on-board FIRs to generate more, smaller, sub-bands for VLBI recording.

The figure shows control PC or CompactPCI computers that control the main boards via mezzanine MCB (Monitor & Control Bus) Interface Modules. The current plan is to use the MCB mezzanine card that NRAO is developing for other array systems for this module, and that the communications to the external computer be via 100 Mbit/sec Ethernet. Data out of the Baseline Board is transmitted on a FPDP interface to external data handling computers that are shown in the figure as PCs or CompactPCI boxes. However, any appropriate back-end computer with a FPDP interface could be used. Refer to section 7.4.1 for a more complete discussion of the computing configuration.

#### 2.1 Flexibilities

The correlator architecture is very flexible and there are a number of dynamic tradeoffs that can be made that may not be evident from the above description. Some of these "flexibilities" are as follows:

- Tradeoff number of antennas for bandwidth. Since each baseband input on each Station Board has its own delay compensation, it is possible to use more Station Boards per antenna to increase bandwidth, or use fewer Station Boards per antenna to increase the number of antennas processed but with decreased bandwidth. Implementing this flexibility dynamically requires a fiber-optic switch in front of the Station Boards, but it does not require any internal correlator rewiring.

- Tradeoff bandwidth for number of beams on the sky. Each baseband input can be used to place a beam anywhere on the sky. This can be useful for post-correlation interference cancellation where it is desired to place one beam on the radio source, and one beam on the interference source *using the same data*. Within a baseband, each FIR filter can place a sub-band beam within ~0.25° (depending on the maximum baseline) of the baseband beam.

- Deploy spectral channel resources as desired. Each sub-band can be any width and placement within the baseband within its "slot" constraints [0]. The switch on the output of the Station Board can route the same data to multiple sub-band correlators and so there are numerous ways that spectral channel resources can be allocated to sub-bands. With recirculation, sub-bands narrower than 128 MHz see an (inversely proportional) increase in the number of spectral channels available to them.

- Tradeoff baseband bandwidth for number of basebands. Each baseband input can handle 2 GHz of total bandwidth at 4 bits per sample. This requires a "data highway" that is 64 bits wide, at 256 Mbits/sec each. This data highway can be used for multiple narrower baseband inputs in varying combinations.

- **Data routing supports expansion**. There is a linear increase in the number of Baseline Boards that a particular sub-band cable must be fed to with increasing

number of stations. The design permits expansion without having to replace the existing infrastructure.

- Data routing allows different correlator configurations. Because sub-band data is routed to Baseline Boards with cable, it is possible to configure the data routing to support varying configurations. (Examples: big antenna multi-beams, with small antenna single beam; little-big antenna correlations, but not little-little antenna correlations.)

- Unlimited interferometer sub-arraying. Each sub-array can be operated with completely independent parameters within the capabilities of the hardware since each station is processed independently.

- **Phased sub-arraying can be different for each sub-band**. Each Phasing Board can be set independently of other Phasing Boards.

### 3 Station Board

The Station Board shown in the module connectivity diagram of Figure 2-1 is where all station-based processing happens in the correlator. Each Station Board processes two, 2 GHz sampled basebands and there are four Station Boards for each "station input" into the correlator. A detailed block diagram of the Station Board is shown in Figure 3-1.

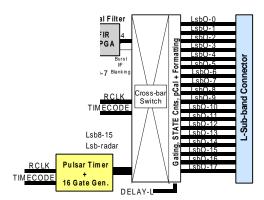

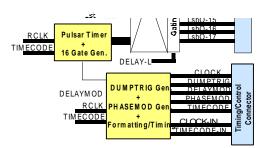

**Figure 3-1** Detailed Station Board functional block diagram. Data enters via the FOTS Rx Modules, is delayed to compensate for wavefront delay, is filtered into sub-bands with digital filters, and then exits via a switch for further processing. A detailed description of each block is given in the following sub-sections.

The Station Board receives data from an antenna via a FOTS receiver module, compensates for wavefront delay, digitally filters the wideband data into sub-bands using FIR filters, and then formats the data for further downstream processing. The Station Board also generates all of the additional information such as DUMPTRIG, DELAYMOD, and PHASEMOD that travels with the data for further downstream processing. These additional signals are described in detail in section 4.1.1. Each block in Figure 3-1 will be described in more detail in the following sub-sections.

## 3.1 FOTS Rx Module(s)

This mezzanine module will be developed by NRAO as part of the FOTS (Fiber-Optic Transmission System) for the EVLA and will plug into the Station Board motherboard. There could be one module for each (2 GHz) baseband input (as shown in the figure) or there could be one module for both inputs. The physical input to the module is fiber via blindmate fiber connectors. There may be additional inputs—for monitor and control purposes independent of the Station Board—and these must use blind-mate connectors as well, otherwise the Station Board can not be inserted as planned.

The module contains the fiber receivers and all of the circuitry for word alignment and error detection/monitoring that are not of concern to the Station Board but are required to ensure link integrity. The module also contains test vector/BERT (Bit Error Rate Test) generation circuitry that allows testing of the module's connection to Station Board circuitry. The method used for invoking this testing capability is TBD.

The signals at the mezzanine card interface connector (which mates with the Station Board) contain 64 bit streams at 256 Mbits/sec each, a synchronous clock, and a synchronization time tick. The clock and data are synchronous and recovered from the fiber signal. The clock and data are generally not phase synchronous<sup>2</sup> with Station Board clocks and signals. The data are nominally arranged as 16 time-demultiplexed sampled data streams, with 4 bits/stream for a total sample rate of 4 Gs/sec<sup>3</sup>. Nominal functional timing is illustrated in Figure 3-2. Performance timing parameters, the number of data valid lines present, and the exact functional and physical interface definition are TBD. Note that other arrangements permitting more, narrower basebands are possible but the clock will always operate at a nominal 128 MHz. If lower bit rate data is present, then data streams will change states in accordance with their sample rates, but synchronous to

<sup>&</sup>lt;sup>3</sup> More correctly it is 4.096 Gs/s, but referred to as 4 Gs/s throughout the document.

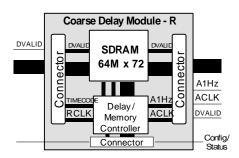

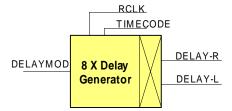

<sup>&</sup>lt;sup>2</sup> Or even phase stable because of receiver phase locking and because this could be data from a VLBI recorder.