# **EVLA Correlator Prototype and OTS Testing** *B. Carlson*

National Research CouncilConseil national de recherchesCanadaCanada

EVLA Correlator S/W F2F Apr 3-4, 2006

#### Outline

- Initial prototype testing.

- Test setups.

- Test equipment.

- Prototype system testing.

- On-the-Sky (OTS) testing.

- Review of DRAFT test plan.

- Schedule.

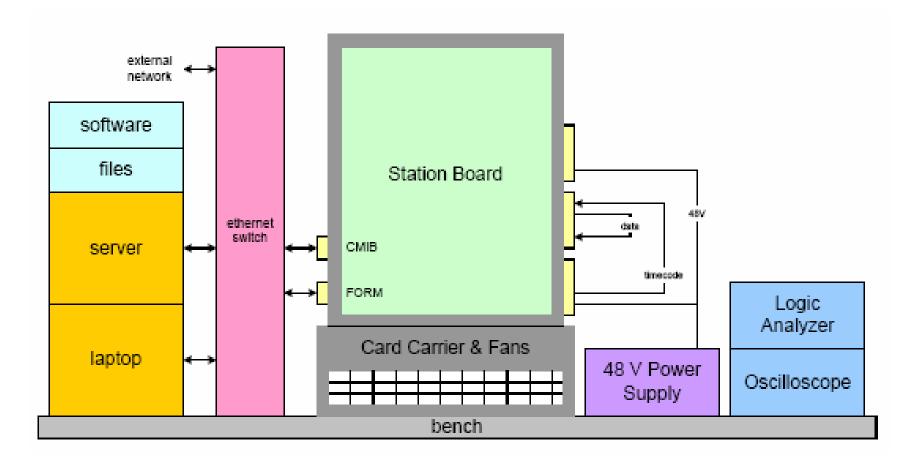

#### **Initial Prototype Testing**

- Station Board and Baseline Board tested separately.

- Station Board contains its own timing, test vector generators, and has loopback test capability for testing HM Gbps.

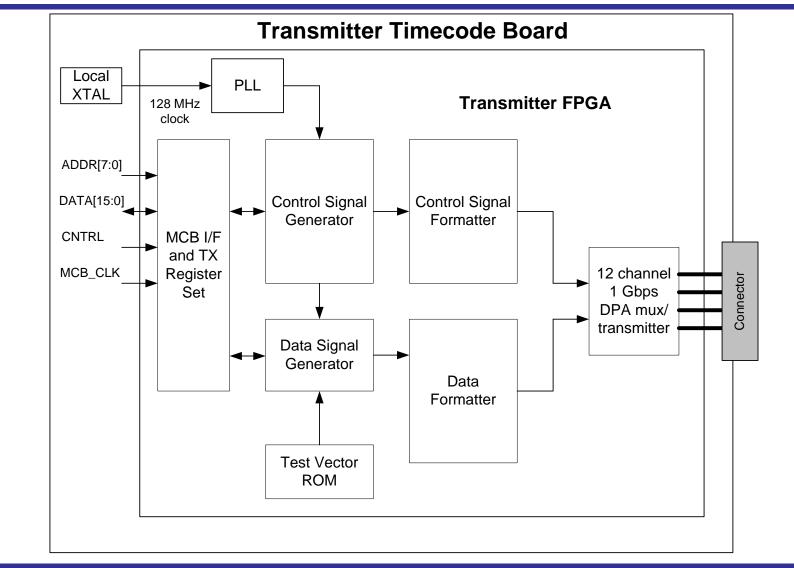

- Baseline Board stimulated with a Timecode Board.

- TGB FPGA special design used to generate HM Gbps signals for testing.

- Prototype Corr Chips socketed...all sites can be tested...some risk.

- Formal qualification of Corr Chips before full ASIC production (hopefully in '06).

#### TVP: A25040N0003

EVLA Correlator S/W F2F - Prototype testing

EVLA Correlator S/W F2F - Prototype testing

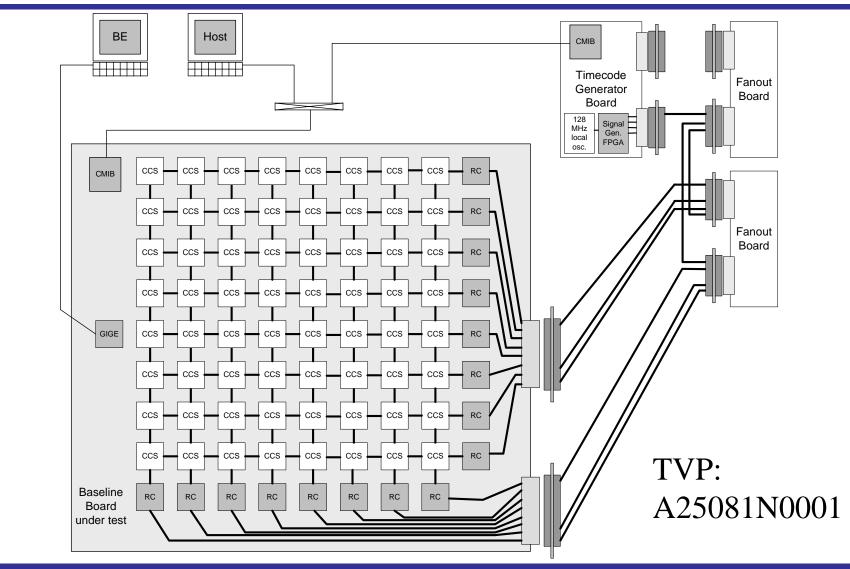

#### **Baseline Board proto testing**

• Description of test vectors, GUI panels, CBE requirements in appendix of Correlator Chip prototype verification matrix document A25082N0005 (in prep, no DRAFT release yet).

| Timing and Dump Control |                   |                  |            |           |                                      |                  |       |                |                                          |            |  |  |  |  |

|-------------------------|-------------------|------------------|------------|-----------|--------------------------------------|------------------|-------|----------------|------------------------------------------|------------|--|--|--|--|

| Enabl                   | e TIMEC           | ODE<br>ODE peric | od (usec)  |           | Data Stream Control                  |                  |       |                |                                          |            |  |  |  |  |

|                         | THME O            |                  | (u000)     |           | 256 Sample rate Ms/s PHASEMOD Models |                  |       |                |                                          |            |  |  |  |  |

| DUMI                    | PTRIG E           | nable            |            |           |                                      | DATA             | Strea | am IDS         | 🖂 hex 📋 decimal                          | Hz, cycles |  |  |  |  |

|                         | Sync Tes          | t Eramo          |            |           |                                      | SID              | SBID  | BBID           | P0                                       | P1         |  |  |  |  |

|                         | •                 |                  |            |           | DATA-0                               | 105              | 3     | 0              | 03026EFB                                 | 00259506   |  |  |  |  |

|                         | Speed du          | imps             |            |           | DATA-1                               | 115              | 5     | 1              | 0D416D36                                 | 00A58873   |  |  |  |  |

|                         | Normal d          | umps             |            |           | DATA-2                               | 125              | 7     | 2              | 05B36D8B                                 | 0047310D   |  |  |  |  |

| _                       |                   |                  |            |           | DATA-3                               | 135              | 9     | 3              | 1A060683                                 | 0144FA12   |  |  |  |  |

|                         | UMPTRIG<br>Period | Dump             | LTA        | Frames/s/ | DATA-4                               | 145              | 11    | 4              | 08646C1B                                 | 0068CD14   |  |  |  |  |

| DATA str                | (usec)            | Modulo           | accum      | CCC/chip  | DATA-5                               | 155              | 13    | 5              | 26CA9FCF                                 | 01E46BB2   |  |  |  |  |

| DATA-0                  | 20                | 4                | 100        | 500       | DATA-6                               | 165              | 15    | 008A691B       |                                          |            |  |  |  |  |

|                         |                   |                  |            | 405       | DATA-7                               | 175              | 17    | 7              | 338F391C                                 | 0283DD52   |  |  |  |  |

| DATA-1<br>DATA-2        | 40<br>60          | 8                | 200<br>300 | 125<br>56 | PHASERR                              | _m (0,2          | ,4,6) | 64             | Auto-calc<br>PHASEMOD<br>Re-Calculate PH | D coeffs   |  |  |  |  |

| DATA-3                  | 80                | 16               | 400        | 31        | PHASERR                              | _n (1,3          | ,5,7) | 64             | coeffs for current s                     |            |  |  |  |  |

| DATA-4                  | 100               | 20               | 500        | 20        |                                      |                  |       |                | or Generation                            | _          |  |  |  |  |

| DATA-5                  | 120               | 24               | 600        | 14        |                                      | CODE<br>PTRIG    |       | PHASE<br>PHASE | RR6_7 DATA-                              | 1 🗌 DATA-5 |  |  |  |  |

| DATA-6                  | 140               | 28               | 700        | 10        |                                      | SERR0_<br>SERR2_ |       | PHASE          | MOD DATA-2<br>DATA-3                     |            |  |  |  |  |

| DATA-7                  | 160               | 32               | 800        | 8         | L                                    |                  |       |                |                                          |            |  |  |  |  |

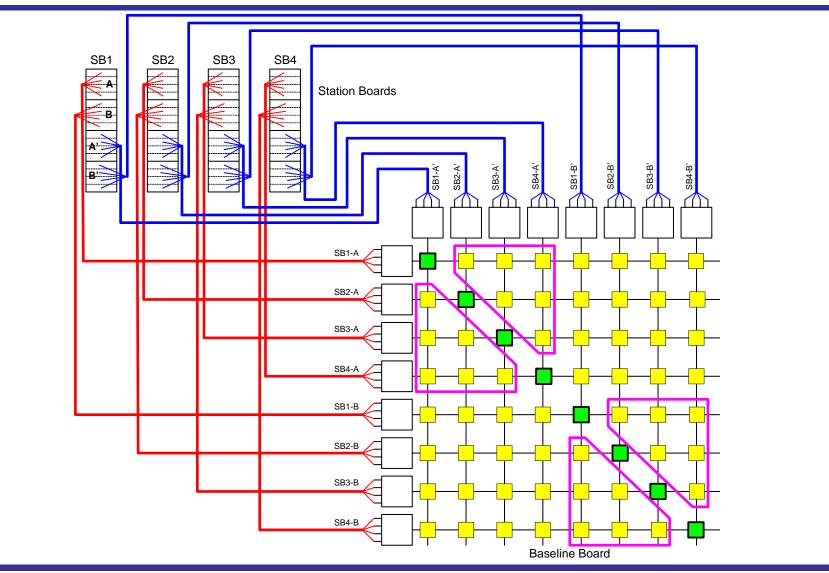

#### **Baseline Board**

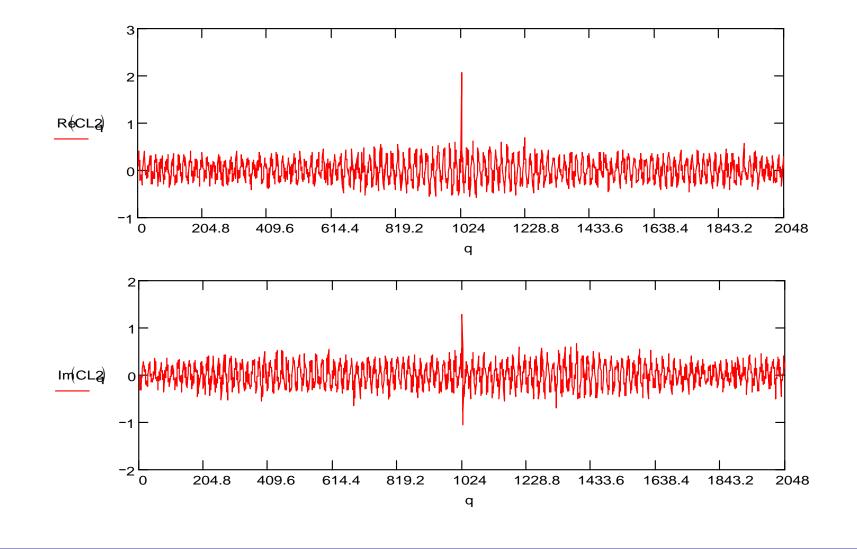

- Raw frames from CBE inspected for correctness.

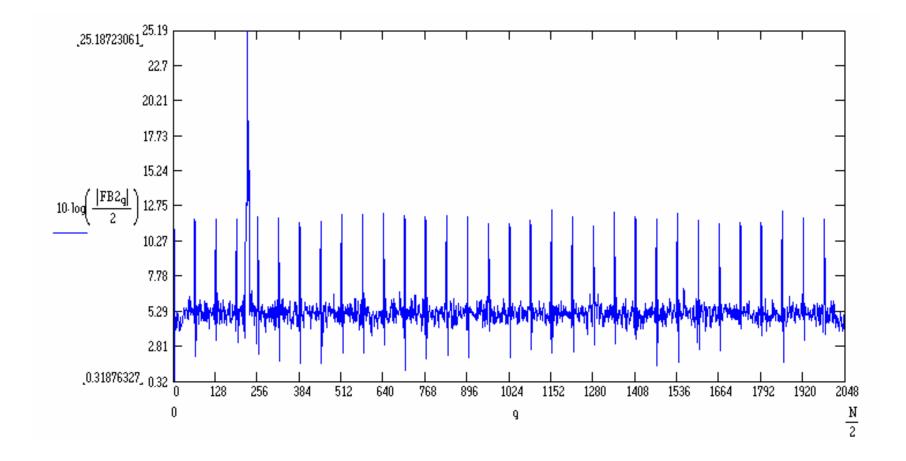

- Plots from CBE...cross-correlation of vectors generated by TGB special FPGA (should) produce fringes.

- Vectors support bit-exact comparison of hardware via CBE's raw floatingpoint Re/Im lags with S/W reference correlator.

- Don't need to use Corr Chip RTL simulation (slow).

- Not quite bit-exact—within double-precision floating-point numerical error.

- Also, perform redundant correlations...compare with each other.

####

W0: START SYNC WORD -- OK aaaaaaaa W1: B31=ASIC[1] Yin=1 Xin=1 YSyner=0 XSyner=0 ACC\_OV=0 OVR=0 Rsrv=000000 NUM\_CLAGS= 128 CCC=13 Cmmd=010 e001006a 076423c8 W2: BBID-Y=0 SBID-Y= 7 SID-Y=100 BBID-X=1 SBID-X= 3 SID-X=200 d972e900 W3: LTA/Phase bin=55666 Recirc\_blk-Y=233 Recirc\_blk-X= 0 0d408a04 W4: TIMESTAMP-0= 222333444 W5: TIMESTAMP-1= 555666777 211ecd59 00000869 2153 W6: DVCOUNT-Cntr= W7: DVCOUNT-Edge= 2119 00000847 0003a300 W8: DATA\_BIAS 238336 = 0003a545 238917 0 = Lag 0003a3e6 Laq 0 = 238566 0003a5f8 Lag 1 = 239096 0003a3d8 238552 Lag 1 = 0003a370 2 = 238448 Lag 0003alfa Lag 2 = 238074 0003a3a6 Lag 3 = 238502 0003a078 Laq 3 = 237688 0003a2af Laq 4 = 238255 0003a1d2 4 = 238034 Lag 0003a2ce 5 = 238286 Lag 0003a268 Lag 5 = 238184 CBE raw frame output 0003a3b6 Laq б = 238518 0003a256 Lag б = 238166 0003a1fc 7 = 238076 Lag 0003a1fa Laq 7 = 238074 . 0003a20a Lag 125 = 238090 Lag 125 = 0003a3fe 238590 0003a6cc Lag 126 = 239308 0003a57c Lag 126 = 238972 Lag 127 = 0003a550 238928 0003a418 Lag 127 = 238616 W265: END SYNC WORD -- OK 1c71c71c

B. Carlson, 2006-Apr 3-4

W266: Checksum calculated OK

b9fa8535

- 1.675218060543869e-01 -1.723961005643920e-01 3.732683427398666e-02 -5.438686505900462e-02 1.282709081580298e-03

- -1.918932786044125e-01 -1.096716264751154e-01 5.246280143663417e-02

- CBE raw floating-point output

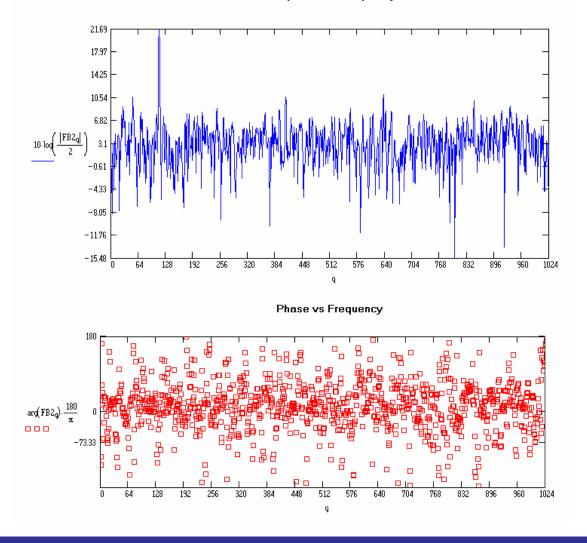

Amplitude vs Frequency

B. Carlson, 2006-Apr 3-4

EVLA Correlator S/W F2F - Prototype testing

#### **Test Equipment**

- Agilent 16900A/16950A logic analyser.

- 64 channels, 600 MHz state, 4 GHz timing.

- Mate with soft-touch probe headers on board.

- 4 test pins out of FPGAs.

- Agilent Infineon **Digital Storage Oscilloscope**.

- 4 channels, 20 Gs/s/channel. 7 GHz bandwidth.

- 2 differential or single-ended probes.

- Probing...difficult due to speed, signal integrity, routing density...use signal vias...special probing kits.

- Jitter analysis software.

- X-ray machine, BGA re-work machine.

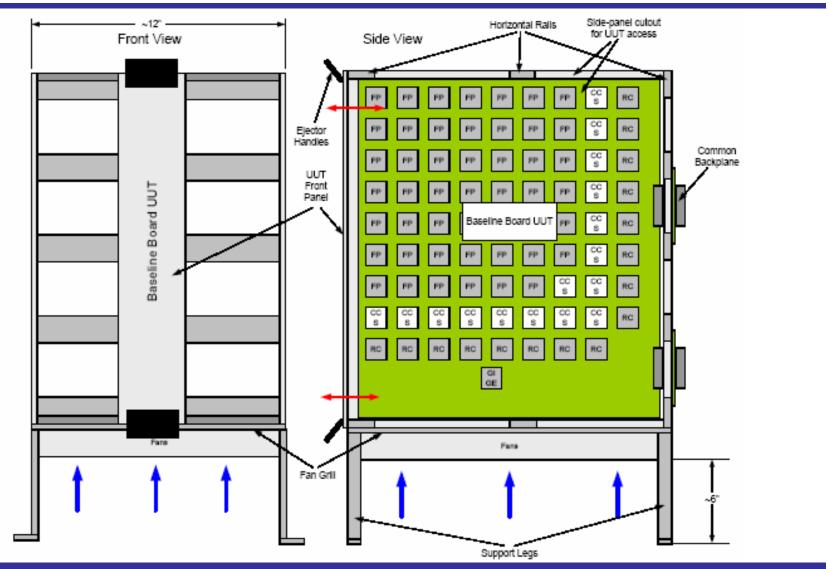

#### **Prototype System Testing**

- Connect Station Board outputs to Baseline Board inputs.

- Establish/test HM Gbps connectivity.

- Delay Module test vectors stimulate Station Board and downstream Baseline Board.

- Compare results with software filter/correlator that processes the same test vectors.

- Not bit-exact comparison...statistical only.

#### **On-the-Sky Testing (OTS)**

- DRAFT Test Plan A25010N0005.

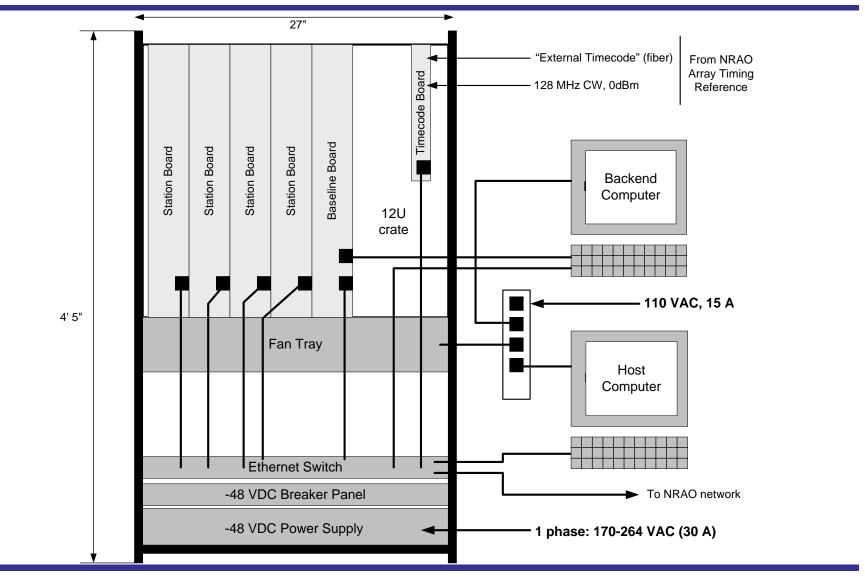

- Prototype correlator test setup.

- 45 tests. Specified in plan in an overview fashion. Details filled in with GUIs/configuration files.

- Digital tone comb generator in DTS Tx or Rx or Station Board Input Chip useful...for detecting timing/delay tracking hiccups with Filter Chip tone extractor.

EVLA Correlator S/W F2F - Prototype testing

| TEST | Purpose of Test                                                                               | Description/Test Setup                                                                                                                                                                                                                                                    | Expected Outcome                                                                                                        | Notes                                                                                                                                                         |

|------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Shipping damage check,<br>prototype correlator<br>installation and setup.                     | Unpack system, check for damage, install boards.<br>Install system in test location.                                                                                                                                                                                      | All components available and<br>undamaged. System installation<br>successful.                                           | Some assembly required.                                                                                                                                       |

| 1    | System power-up and self-<br>check with local 128 MHz<br>oscillator on the Timecode<br>Board. | Connect AC power to -48 VDC power supply.<br>Connect AC power to to AC-powered components.<br>Power-up system, use the Timecode local crystal<br>oscillator. Perform Station Board checks. Perform<br>Baseline Board checks. Check connectivity of<br>Station-to-Baseline | All self-checks and functions ok.<br>Backend receives frames. RTDD can<br>display data products.                        | No antennas are<br>required.                                                                                                                                  |

| 2    | Computer network setup<br>and check.                                                          | The Host Computer must be connected to the<br>embedded processors via the switch. The switch<br>is connected to the NRAO network to allow for time<br>setting (or this setting may be manual via a control<br>computer GUI), and for connection to Model Server.          |                                                                                                                         | The control computer<br>sets correlator<br>configurations. The only<br>connection to EVLA<br>M&C is the Model Server<br>and, optionally, the time<br>setting. |

| 3    | Run self-checks with<br>connection to NRAO<br>"External Timecode", and<br>128 MHz 0 dBm CW.   | Same as TEST 1, except use NRAO time<br>reference. Check for timing synchronization of<br>TIMECODE to array UTC.                                                                                                                                                          | TIMECODE synchronized to NRAO<br>UTC. Phase-lock achieved on all chips<br>on all boards. All intra-system checks<br>ok. | No antennas required.                                                                                                                                         |

| 11 | First fringe test, single,<br>short baseline, 8-bit, 4-bit re-<br>quantization. One sub-<br>band. One antenna should<br>be "Reference Antenna",<br>with well-known LO fiber<br>delay. | Set RF to C-band for minimal interference. Set<br>antenna differential frequency shift to 1 kHz.<br>Observe and track strong continuum source. Turn<br>on digital tone comb generator in DTS transmitter.<br>Turn on one sub-band filter at the center of the<br>wideband. | Stable phase-cal ampl and phase vs<br>time, with delay tracking active. State<br>counts, auto-spectra, power<br>measurements within normal regions.<br>Cross-correlation fringes detected,<br>displayed with RTDD. Ampl and phase<br>vs frequency as expected. SNR as<br>expecte | This test requires 2<br>antennas, possibly for an<br>extended period of time.                                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | First fringe check compared<br>with old correlator, short<br>baseline.                                                                                                                | •                                                                                                                                                                                                                                                                          | Check SNR and normalized amplitudes.<br>Check spectrum. Check and compare<br>with AIPS.                                                                                                                                                                                          | This test requires 2<br>antennas for a short<br>period for the observation.<br>Comparison of old and<br>new correlator can be<br>performed off-line. |

| 13 | Fringe test, single, short<br>baseline, 3-bit, 4-bit re-<br>quantization. One sub-<br>band.                                                                                           | Set RF to X-band for full 2 GHz bandwidth. Set<br>differential frequency shift to 1 kHz. Observe and<br>track strong continuum source. Turn on digital<br>tone comb generator in DTS transmitter. Turn on<br>one sub-band filter at the center of the wideband.<br>Turn o  | Stable phase-cal ampl and phase vs<br>time, with delay tracking active. State<br>counts, auto-spectra, power<br>measurements within normal regions.<br>Cross-correlation fringes detected,<br>displayed with RTDD. Ampl and phase<br>vs frequency as expected. SNR as<br>expecte | This test requires 2<br>antennas, possibly for an<br>extended period of time.                                                                        |

| 31    | High SNR solar observation.                                                                                                                                                                                                              | Correlator settings as required by astronomy teams, possibly incorporating "wideband recirculation". Possibly requiring 64 lags per CCC output mode from correlator.                                         | Results as required by astronomy teams.                                 | This test requires 4<br>antennas for the duration<br>of the experiment.                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 32    | Narrowband, high-spectral resolution.                                                                                                                                                                                                    | Maximum spectral resolution on desired sub-band<br>bandwidth. Possibly 1 Hz resolution. Correlator<br>settings, number of antennas, set by astronomy<br>team. Try to exercise all stages in the Filter Chip. | Results as required by astronomy teams.                                 | This test requires 4<br>antennas for the duration<br>of the experiment.                                |

| 33    | Radar-mode data capture.                                                                                                                                                                                                                 | Set sub-band for capture to 31.25 kHz. Capture<br>data into NFS files. Use Filter Chip Stage 2 mixer<br>to stop fringes and very-fine delay tracking.<br>Observe spectral-line source with continuum.        | Correlate captured data in software.<br>Ensure results are as expected. | This test requires 4<br>antennas for the duration<br>of the data capture<br>portion of the experiment. |

| 34-44 | Astronomer-driven key<br>science experiments of<br>various kinds: continuum,<br>high dynamic range spectral-<br>line, mixed continuum and<br>spectral-line, pulsar,<br>recirculation, fast dumping,<br>long integrations, radar<br>mode. |                                                                                                                                                                                                              |                                                                         |                                                                                                        |

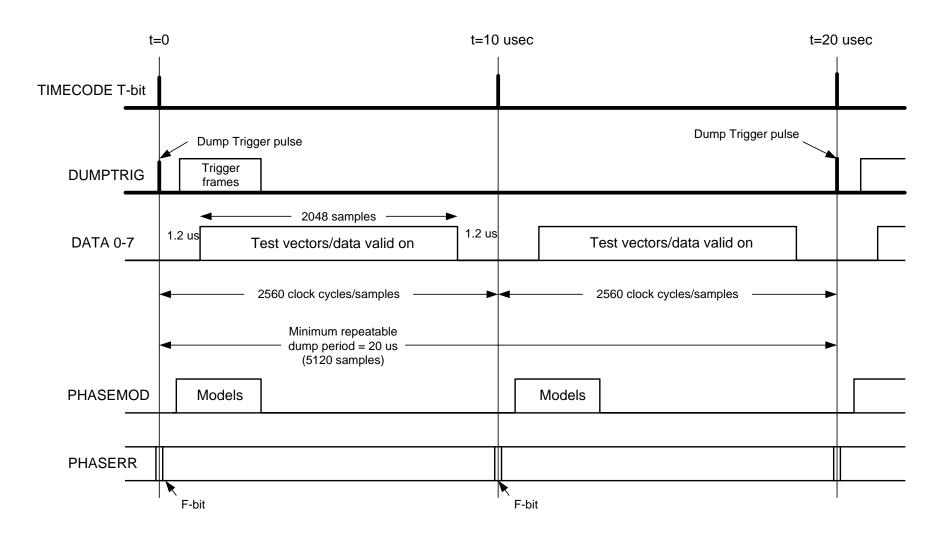

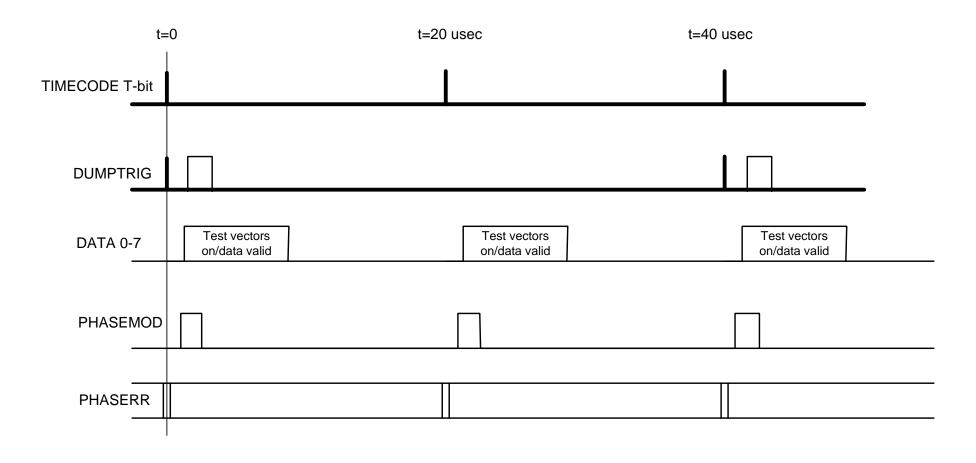

## OTS

- Station Board real-time S/W *critical* for OTS testing.

- Delay tracking...models from NRAO "Model Server".

- Phase model generation.

- Dump control (DUMPTRIG) generation.

- Acquisition of state counts, wideband correlation coefficients, etc.

- "Programmer's Guide" (A25290N0000) contains comprehensive information on many low-level real-time functions that software needs to control.

## OTS

- Many tests require science input and work for source selection and image processing/data analysis.

- Last 10 tests are completely astronomer-driven experiments of various kinds.

- OTS testing not used to qualify hardware for Stage 3 production. Used to demonstrate correlator functionality, provide "early"-use correlator, 1<sup>st</sup> step in total system integration testing.

#### Schedule

- Many unquantifiable uncertainties/risks. Have paid in \$, time, and tools to minimize risks as much as possible.

- Allocated ~6 months for initial prototype testing.

- Another ~6 months for getting proto corrs for OTS ready.

- ~4 months for OTS testing.

- ~Nov. 15/06 deadline for decision on Corr chip production in FY 06/07. Currently \$ not in FY 06/07 budget.

| 1 | Task Name                                         | 04 '05 | 2006  | 3 02 0 | 08 03 08 |       | 2007  | 02 '07 | 03.07 04. | 200 |            | 2 108 0 | 03.08   | 34 '02 | 2009  | 02 100 | Q3 109 Q4 1 | 20 |

|---|---------------------------------------------------|--------|-------|--------|----------|-------|-------|--------|-----------|-----|------------|---------|---------|--------|-------|--------|-------------|----|

|   | Stage 1 Prototype Hardware in Penticton           | 4 05   | Garbe | 5 42 0 |          | 00 40 | QL U/ | Q2 U7  | 4507 44   |     | 00 1 4     | 2 00 1  | 45 00 1 | 24 00  | QT 08 | 42.08  | 45 08 04 0  |    |

|   | Stage 1 Prototype PCB Acceptance Testing          |        |       |        |          | h     |       |        |           |     |            |         |         |        |       |        |             |    |

| 3 | Stage 2 Prototype Fabrication & Assembly          |        |       |        |          | Ľ     | h     |        |           |     |            |         |         |        |       |        |             |    |

|   | Hardware/Software Integration Testing             |        |       |        |          |       | Ľ     |        | 1         |     |            |         |         |        |       |        |             |    |

|   | Critical Design Review                            |        |       |        |          |       | 1     | -      | 26/06     |     |            |         |         |        |       |        |             |    |

| - | Hardware for OTS Testing Sent to VLA              |        |       |        |          |       |       | [      |           |     |            |         |         |        |       |        |             |    |

| _ | On-The-Sky Testing                                |        |       |        |          |       |       |        |           |     |            |         |         |        |       |        |             |    |

|   | Stage 3 Production Hardware                       |        |       |        |          |       |       | [      | *h        |     |            |         |         |        |       |        |             |    |

|   | System Integration & Testing @ Penticton          |        |       |        |          |       |       |        |           |     | 1          |         |         |        |       |        |             |    |

|   | Limited Production Hardware Sent to VLA           |        |       |        |          |       |       |        |           | i i | <b>b</b> - |         |         |        |       |        |             |    |

|   | Stage 4 Production Hardware                       |        |       |        |          |       |       |        |           |     |            | Ъ       |         |        |       |        |             |    |

|   | Final Full Production Test & Burn-in in Penticton |        |       |        |          |       |       |        |           |     |            | t       | Ъ       |        |       |        |             |    |

|   | Full Board Installation & Testing @ VLA           |        |       |        |          |       |       |        |           |     |            |         | Ť       |        |       |        | _h          |    |

| _ | Commissioning - Turn off old correlator           |        |       |        | <u> </u> |       |       |        |           |     |            |         | 1       |        |       |        | <b>*</b>    |    |

| - | Prototype Software                                |        |       |        |          |       |       |        |           |     |            |         |         |        |       |        | 1           |    |

|   | MCCC Software                                     |        |       |        |          |       |       |        |           |     |            |         | _       |        |       |        |             |    |

|   | CPCC Software                                     |        |       |        |          |       |       |        |           |     |            |         | _       |        |       |        |             |    |

| _ | Correlator Backend Software (V1.0 Test, V2.0)     |        |       |        |          |       |       |        |           |     |            |         | -       |        |       |        |             |    |

|   | CMIB Production Software                          |        |       |        |          |       |       |        | _         |     |            |         |         |        |       |        |             |    |