# **Technical Benefits and Difficulties** *B. Carlson*

####

# Outline

- Technical benefits.

- Fewer Baseline Boards, racks.

- 3X fewer hi-speed cables.

- More logical/seamless phasing capability...all bandwidth all the time.

- Technical difficulties/uncertainties.

- Re-timing hops.

- Y Recirc FPGA connections for Tx or Rx (expansion).

- Y connector out to X in via patch board.

- DC biasing on re-timing FPGA inputs.

- Re-timing FPGA connections; 2 x 80 lines at 512 Mbps DDR.

- 1:2 LVDS buffers...small package...rework specialty.

- Phasing design not yet done...logic use estimates.

# **Technical Benefits**

- 3X fewer cables: 3X fewer cable contacts...3X more reliable.

- Vastly simpler baseline rack wiring (almost empty).

- Simpler rack-to-rack and intra-rack wiring

- Only 64 short cables in each station rack, rather then 160 short cables in each baseline rack.

- Rack-to-rack wiring is point-to-point...easier site installation.

- Kit with 128 bunches of 4 cables going rack-to-rack, rather than 512 individual cables.

#### NRC · CNRC

B. Carlson, 2007-Jul 31

Technical benefits and difficulties

# **Technical Benefits**

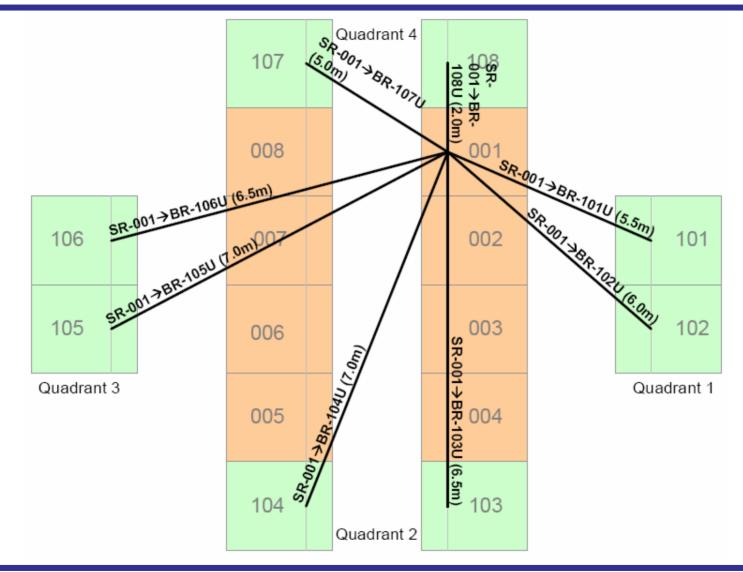

- Maximum cable length is now 7 m...better eye at the receiving end.

- Station Board outputs have to drive only 1 m of cable. X-bar board drives long cable with high-voltage PECL drivers.

- Reduces the number of baseline racks from 16 to 8...more room in correlator room for other equipment/expansion.

- Reduces the number of Baseline Boards from 160 to 128...more reliable system.

# **Technical Benefits**

- More logically consistent and dynamically available phasing...several options for getting data to VLBI recording equipment.

- VLBI recording equipment can sit in racks beside baseline racks...or elsewhere, depending on interface.

- Connect all streams into Station Board(s) that, via VSI-H output, goes to VLBI recorder (or iBob board to 10 GigE) (previous talk for details).

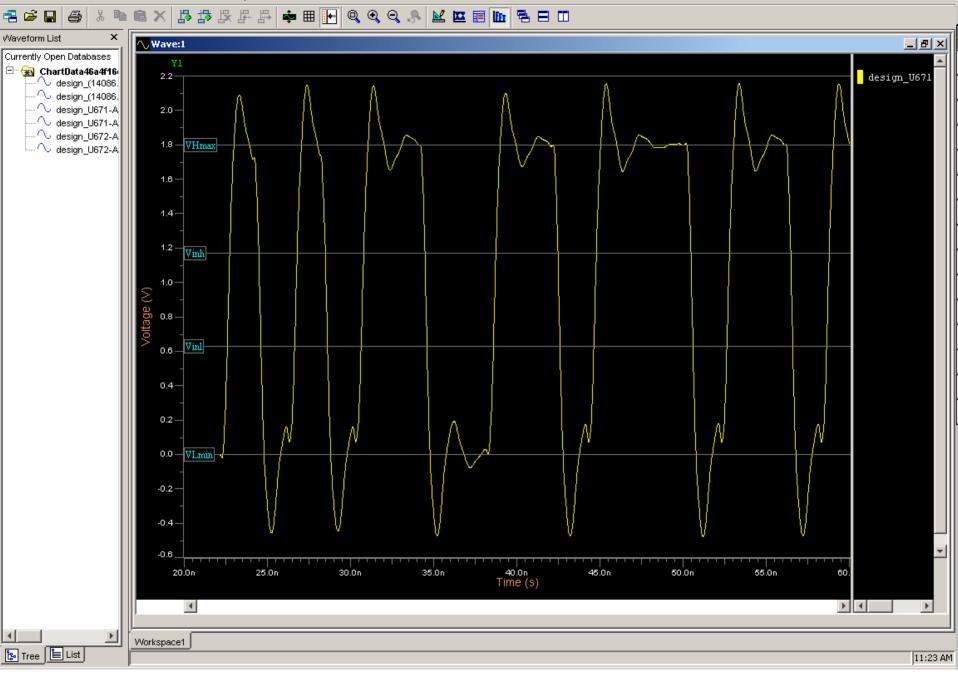

- Starting at the Station Board, there are 5 "hops"/re-timings of the signal before it gets to the last Recirc FPGA on the 2<sup>nd</sup> Baseline Board.

- Low-level worry this might be a problem...you never know!

- FPGA PLLs perform very well...currently testing 3 hops under worse conditions (longer cables between hops) than in the new scheme.

- FPGA PLLs set for low bandwidth, max jitter rejection. 128 MHz clock jitter accumulation low compared to 1 Gbps anyway.

- Backup plan:

- Provide external clock input to each Station and Baseline Board via blind-mate SMA connector at the rear of the board.

- If clock jitter becomes a problem when the whole system is together, could reasonably easily add external clock network by adding SMA bulkheads, splitter, amplifier...take more work to make it fault-tolerant redundant (that's why we dropped doing this in the first place).

- The Y Recirc FPGAs have 1 Gbps Tx and Rx pins tied together on the outer layer of the PCB to allow for expansion:

- Normally operate as a transmitter...so the Rx pins to Hi-z receiver in the FPGA are a stub (~1", including PCB, FPGA ~350 psec RT)

- When operated as a receiver (expansion), the Tx pins to Hi-z transmitter in the FPGA are a stub (~0.5", including PCB, FPGA ~175 psec RT)

- Could be signal integrity problem (round-trip is ~350 psec).

- Signal integrity on routed board with IS\_analyzer...

- If a problem, 1 board will work anyway; could cut traces to make 2 boards work...replace Tx/Rx connections with 0201 resistor pads in next proto round if necessary. Install resistors to use receivers for expansion.

| 💆 Ехрес                                 | lition I        | PCB -        | Pinna         | cle D               | \EVL                   | A\Se          | cond        | itage        | \Proj         | ect\B          | aselin         | e_B        | oard-' | ¥2.0`     | Base              | lineBo   | ard-¥2      | 2.0Ma | ar26_1     | 07-001\PC        | 8\Baselin        | e_Boar | d.pcb    | Baselin   | e_Board]   |         |          |              | _            | Ð    |

|-----------------------------------------|-----------------|--------------|---------------|---------------------|------------------------|---------------|-------------|--------------|---------------|----------------|----------------|------------|--------|-----------|-------------------|----------|-------------|-------|------------|------------------|------------------|--------|----------|-----------|------------|---------|----------|--------------|--------------|------|

| Ne <u>F</u> ile                         | <u>E</u> dit    | <u>V</u> iew | <u>S</u> etup | Place               | e <u>R</u> o           | ute P         | lanes       | Е <u>С</u> О | <u>A</u> nal; | ysis <u>(</u>  |                |            |        |           |                   |          |             |       |            |                  |                  | lee    |          | xy: 14,18 | 1.85, 6,76 | 2.81 d  | lxdy: 10 | ,463.51, 4,3 | 40.41 (th) 📕 | Ð    |

| <b>e</b> 🖻                              |                 | •            | 9. #          | $\square$           | $\underline{\bigcirc}$ | 8             | <b>3</b> ‡  | <b>D</b> ,   | REV NE        |                |                | 1          | ₽      | P         | <b>~</b> <        | 🕩 💙      | DFF         | ₽     | $ \times $ | III   <b>())</b> | <b>#</b> 🛍       |        |          |           |            | •       |          |              |              |      |

| D. #                                    | . <b>22</b> . ( | #   i        | <b>;</b>      | i 🖻                 | <b>⊔</b> ⊔             |               | <b>&gt;</b> | 1            |               | (← →=<br>(← →= | TT :           |            | Displ  | lay So    | hemes             | 3        |             | •     |            |                  |                  |        |          |           |            |         |          |              |              |      |

| ::: >                                   |                 | <b>11</b>    | ն 🥲           | Ŀ                   |                        | }}   <b>;</b> | ¥ 5         | i   5        | 5             | 12             |                | Þ <b>t</b> | ê (    | 3   3     | ≂ ∟               | - 14     | ð 🖌         | 2     | r 20       | Display S        | chemes           |        | •        | 1         |            |         |          |              |              |      |

| ୖୣ୕ୢୄୖ                                  | 0               | $\odot$      |               | $\odot$             | ٢                      |               |             |              |               | $\odot$        | $\odot$        |            |        |           | AND DE CONTRACTOR | 0        |             |       | 0          |                  | <b>O</b> -       | -      | )        |           |            |         |          |              |              |      |

| ି୍ 🏾                                    | 0               | Q            | 0             | $\odot$             | ٢                      | ٢             | ٢           | ٢            |               | $\odot$        | ١              |            |        | Ó         |                   | <b>n</b> |             | ٢     | ۲          |                  | ©-               | -6     | 3)       |           |            |         |          |              |              |      |

| ຼັ⊚                                     | •               | $\odot$      | Ŷ             |                     |                        |               | ۲           | ۲            | ٢             | $\odot$        |                |            | 0      | Ø         | Q                 | Ò        | ۱           | ٢     | ۲          |                  | @ <b>.</b>       | -6     | 3)       |           |            |         |          |              |              |      |

| ð i                                     |                 |              |               | @¤                  | aaad                   | 9             | Q           | ٢            | ۲             | $\odot$        | $\odot$        |            |        |           |                   |          |             | ۲     | ٢          |                  |                  |        | ~        |           |            |         |          |              |              |      |

| ्रे                                     |                 | ۲            |               | State of the second | ()<br>I                | ¢             | Ô           |              |               | 00             | 80<br>90       | ٢          |        | Q         | Ć                 | ø        | 0           | ٢     | ٢          |                  | <b>.</b>         |        | 9)<br>   |           |            |         |          |              |              |      |

|                                         | •               |              |               | ٢                   |                        |               |             |              | œ             |                | 38<br>         | 3          | ۲      | Q         | ۲                 | Ø        | Ó           | ٢     | ۲          |                  | ©F               |        | 3)       |           |            |         |          |              |              |      |

| 0                                       | •               |              |               |                     | Ø                      | -             | 70          | 9            |               |                |                |            |        | ٢         | Ì                 | jo       | 0           | ۲     | ۲          |                  | <b>*</b>         | -      | ۲        |           |            |         |          |              |              |      |

| )<br>                                   | $\odot$         |              | Q,            |                     | $\overline{\odot}$     |               |             |              |               | 0              | 0              | Ø          | 5      | 30        | Ø                 | Q        | 0           | 0     | Q.         |                  | ۵ <mark>۰</mark> | -      | 9        |           |            |         |          |              |              |      |

| 20                                      | J©,             |              | ø             | Ľ                   | ۵,                     | 2             |             |              |               | 0              | đ              | 3          |        |           |                   | Q        | •           | Ø     | ۲          |                  | <b>0</b> -       | -      | ٢        |           |            |         |          |              |              |      |

| ) 🛞                                     |                 |              | ø             | ٢                   | ۲                      | 8             |             | ē            | P             | ۲              | ۲              | ۲          | Å      | ,         |                   | ø        |             |       | ٩¢         |                  | <b>®</b> -       | -6     | 3)       |           |            |         |          |              |              |      |

|                                         |                 |              |               |                     |                        | ۲             |             | 6            | 8             |                |                |            | 1955   | ۲         | 25<br>25          | R        | Ø           |       |            |                  | 6                |        | 3)       |           |            |         |          |              |              |      |

| •                                       |                 | ۲            |               | ۲                   | œ                      | 8             | 0,          |              |               |                |                | 1868       | 888    | <b>20</b> | 8                 |          | ø           | ø     |            |                  | ~ <b>_</b>       |        | )<br>)   |           |            |         |          |              |              |      |

| <u> </u>                                | í©              | ۲            | T             | 0                   | 0                      | 8             |             |              | <b>538</b>    | 7@             | © <sub>é</sub> | ø          |        |           | ۲                 | Í        | Í           | ۲     | ۲          |                  | ()<br>           |        |          |           |            |         |          |              |              |      |

| 0                                       | 0               |              | STREET,       | 8                   | ٢                      |               |             |              | <u>888</u>    | 10             |                |            |        | ٢         | Ć                 |          | <u>-0</u> ) | 0     | ٢          |                  | ۵ <b>۲</b>       |        | 9        |           |            |         |          |              |              |      |

| )<br>O                                  | ۲               |              | ۲             | ٢                   | Q                      | ð.            | đ           |              | ø             | P              | <u>@</u>       |            |        |           |                   | đ        | <u>ø</u>    | 0     | ø          |                  | ٥ <del>،</del>   | ÷.     | 9        |           |            |         |          |              |              |      |

| ×                                       |                 |              | ۲             | 0                   |                        |               | ļ           | ٢            |               | 88             |                | ***        | ***    |           |                   | _đ       | Q           | ۲     | ۹          |                  | <b>*</b>         |        | <b>)</b> |           |            |         |          |              |              |      |

|                                         | Ì               |              |               | ۲                   |                        |               | Ø           |              |               |                |                | 338<br>J   | ***    | Ó         | ۲                 | Ø        | ø           | ٢     | ۲          |                  | 0                |        | 3)       |           |            |         |          |              |              |      |

| -                                       | ·               | ۲            |               |                     | Q                      | 8             | /           | ۲            | ٢             | ٢              |                | Ŷ          | Ś      | ۲         | ۲                 | Ò        |             | ٢     | ۲          |                  | <b>0</b> -       |        | 9        |           |            |         |          |              |              |      |

| ) o                                     |                 | ٢            | ۲             | ٢                   |                        |               | ٢           | ٢            | ۲             | ٢              |                |            | 888    | ٢         | ۲                 |          |             | ۲     | ۲          |                  | (®) <b>-</b>     | -6     | -<br>3)  |           |            |         |          |              |              |      |

| 0_0                                     |                 | ۲            | ۲             | ۲                   | ۲                      | 0             | ٢           | ۲            | ٢             | $\odot$        | ۲              |            | ***    | 0         | ۲                 | 0        | 0           | ٢     | ۲          |                  | ~_               |        |          |           |            |         |          |              |              |      |

| ) ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( | ۲               | ۲            |               | ۲                   | ۲                      |               | ۲           | 8            | 0             | ٢              | ۲              |            |        |           | Ŷ                 |          | ۲           | ٢     | Ø          |                  | ©•               |        |          |           |            |         |          |              |              |      |

| 0                                       | ۲               | ٢            | ۲             | ٢                   | ٢                      | 8             | œ           | 38           | ۲             | ٢              | ٢              | ۲          | 0      | 0         |                   |          | ۲           | ۲     | ۲          |                  | © <b>-</b>       |        | )<br>-   |           |            |         |          |              |              |      |

| ) (O                                    | ۲               | ۲            | ٢             | ٢                   | ٢                      | 0             | ٢           | ٢            | ٢             | ٢              | ٢              | ٢          | 0      | ø         |                   |          |             |       | <u>O</u> I | <b>_</b>         | ۵ <b>-</b>       |        | 9        |           |            |         |          |              |              |      |

| 1 H                                     | elp             | 1            | 2 Far         | nout                | 1                      | 3 Plo         | w / M       | ulti         | 4 T c         | oggle G        | âloss          |            | 5      |           |                   | 6 U      | Indo        |       | 71         | Tune             | 8 Rou            | te     | 9 F      | Reroute   | 10 Pu:     | sh Trac | e        | 11 Gloss     | 12 Place     | e >> |

• ► 🎦 Tree 📔 List

Workspace1

4:39 PM

\_ 8 ×

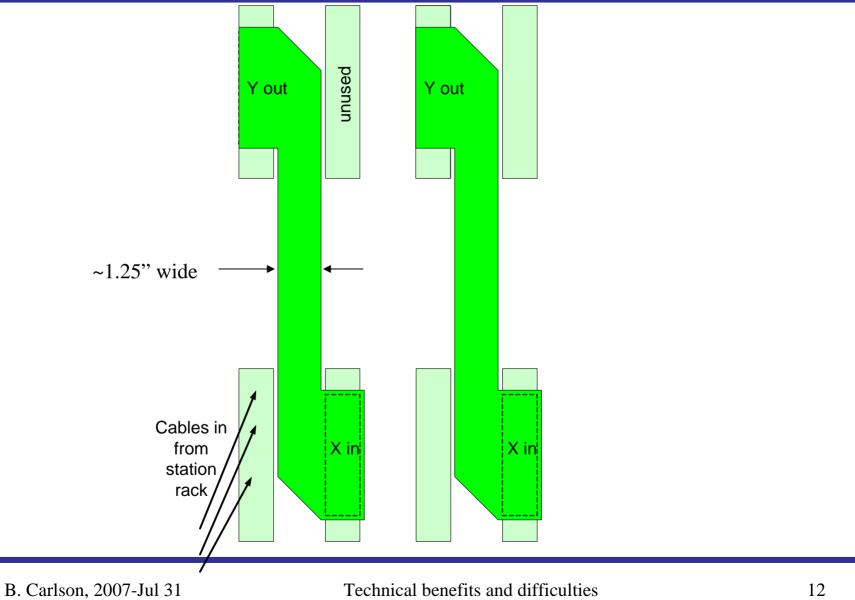

- Y connector out to X in (next board) via patch board.

- Plugs into the Y connector and the X connector of the next board.

- Routes 1 Gbps LVDS signals from Y Recirc FPGAs to next board's re-timing FPGAs max ~19" FR-4 + 2 connectors.

- Use "HyperTransport" output, ~1.6X the output voltage swing (1.2 V differential). Compatible with LVDS on the input.

- Worst case, replace with cable (~8X cost), or better PCB material (?? cost). Use largest traces possible. Use equalization on patch board?

- 28 layers, 14 routing, 14 GND, 128 diff pairs, ~10 diff pairs per layer...should be ok.

- Y7 output routed to X0 input...reorganize with the re-timing FPGA Xbar switch.

- All 1 Gbps transmitters that drive cable are AC-coupled.

- Using on-chip differential termination in the BB re-timing FPGA requires bias to be re-established.

- Can fit only *one* 10 k bias resistor per diff pair on the board...under the connector GND shield.

- Existing Fanout Board had no bias resistor and works ok...although Altera recommends a DC bias. DC leakage input current is 10 μA.

- Will test one bias resistor with the existing Fanout Board.

- If necessary, could put other bias resistor on the X-bar board (at the other end of the cable).

| <mark>≷</mark> Expedition PCB - Pinnacle D:\E¥LA\SecondStage\Project\Baseline_Board-¥2.0\BaselineBoard-¥2.0Mar26_07-001\PCB\Baseline_Board. | pcb - [Baseline_Board]                          | _ 8 ×       |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------|

| Eile Edit View Setup Place Route Planes ECO Analysis Qutput Window Help                                                                     | xy: 14,249.16, 2,654.58 dxdy: 10,530.83, 232.18 | (th) _ 🗗 🗙  |

| 🖙 🖆 🖬 🕪 🖄 🎮 😂 😂 🕼 🚺 🖬 🦾 🏭 📗 🔀 🛷 🎼 🖤 🖑 🕼 🗡 🗮 🛍 👹 🎆 🎒 🚺                                                                                       |                                                 |             |

| ■                                                                                                                                           |                                                 |             |

| 🛱 🍉 飜 ಝ ∿ 🐚    201 🙊 🌮   🛟 55   121 121 121 121 🗇 🗇 🔭 🤍 🐙 🐻   Display Schemes                                                               | -                                               |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

|                                                                                                                                             |                                                 |             |

| 1 Help         2 Fanout         3 Plow / Multi         4 Toggle Gloss         5         6 Undo         7 Tune         8 Route               | 9 Reroute 10 Push Trace 11 Gloss                | 12 Place >> |

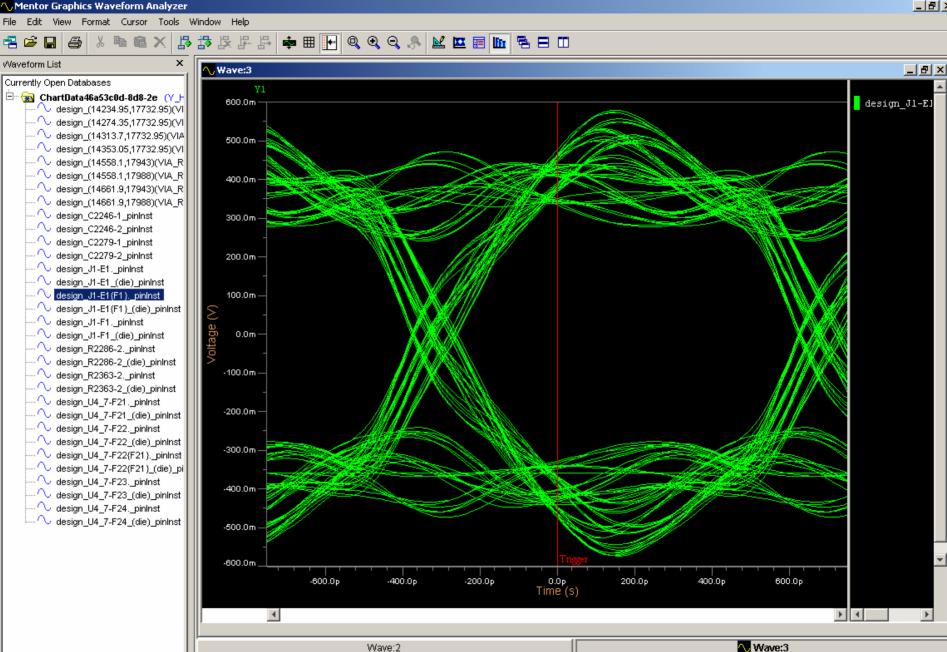

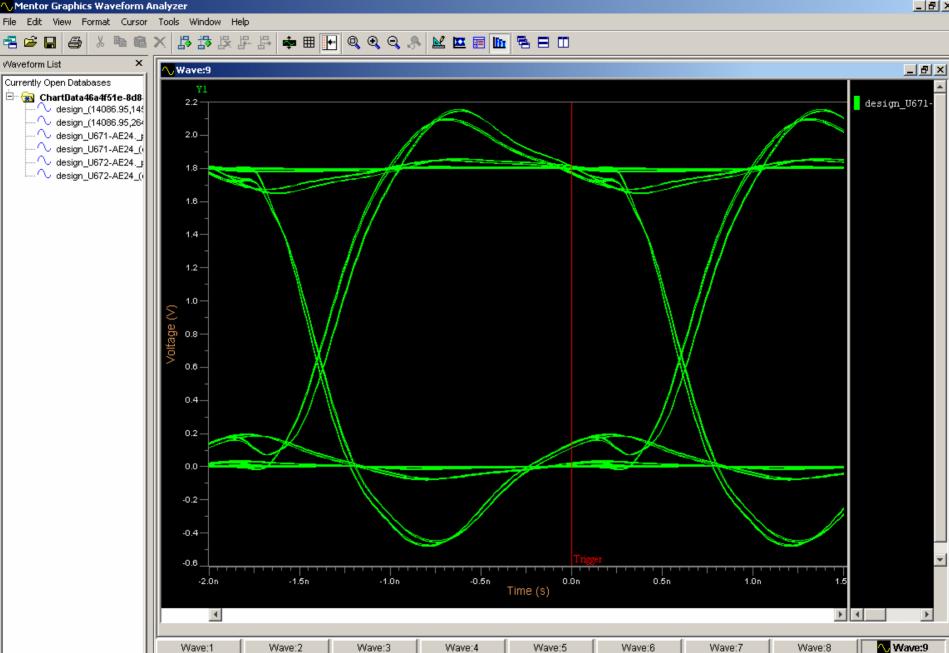

- Between the re-timing FPGAs on the Baseline Board, there are 80 lines going each direction to allow full cross-bar functionality for sub-arrays.

- Each line is 512 Mbps DDR. Lines are short...max ~1.2".

- 1.8 V I/O standard (0.9 V swing)...with 11 pF load (5 pF input, 3.5 pF/in trace capacitance), the FPGA tool says it will work with 10 mA driver (522 Mbps); with 12 mA driver can do 614 Mbps.

#### Nentor Graphics Waveform Analyzer

◀ 🎦 Tree 📔 List

$\mathbf{F}$

Workspace1

11:52 AM

\_ B ×

- 1:2 LVDS fanout buffers after the re-timing FPGAs are in 2 mm x 2 mm package.

- Re-work requires special techniques...use the BGA rework machine, but not the pickup nozzle.

- Requires some additional learning...need to operate the BGA reflow head in manual mode...needs investigation/training.

- Phasing design and PAR not complete yet.

- Estimates (per single-stream phased output):

- Sync + phase gen: ~300 LEs/station = 9600 LEs

- 8-bit complex phase rotation:  $64 \times 256 \times 8$ -bit ROMs = 131k bits.

- 64 8-bit complex multipliers: 64 dedicated 9-bit multipliers.

- 32 x 8-bit complex adder tree: 62 x ~10-bit adders: 700 LEs.

- 128-tap, 8-bit Hilbert transform:

- 128 x 8-bit SRs: 1024 LEs.

- 128 tap coeff mult: 32, 8-bit adders (256 LEs), 32 9-bit multipliers.

- 32 x 9-bit coeff regs: 288 LEs; 31 x ~12-bit adders = 372 LEs

- Re-quantization LUT: 2048 x 8-bit = 16384 RAM bits

- Single-stream phasing estimates (1 phased output):

12,224 LEs, 96 x 9-bit multipliers, 200k RAM bits.

- The re-timing/Xbar requires 12k LEs, 0 RAM, 0 multipliers.

- The EP2S60 chip has ~48 k LEs, 288 9-bit multipliers, 2.5 Mbits RAM.

- With only one phased output per chip, use ~50% LEs, 33% of the multipliers, and 8% of the RAM.

- Seems like each S60 chip might do 2 phased outputs...therefore 4 subarrays/sub-band. Or, S30 for 2 sub-arrays per sub-band??

# Summary

- Technical benefits.

- Fewer Baseline Boards, racks.

- 3X fewer hi-speed cables.

- More logical/seamless phasing capability...all bandwidth all the time.

- Technical difficulties/uncertainties.

- Re-timing hops.

- Y Recirc FPGA connections for Tx or Rx (expansion).

- Y connector out to X in via patch board.

- DC biasing on re-timing FPGA inputs.

- Re-timing FPGA connections; 2 x 80 lines at 512 Mbps DDR.

- 1:2 LVDS buffers...small package...rework specialty.

- Phasing design not yet done...logic use estimates.