### EVLA M&C Transition System Software Critical Design Review December 5-6, 2006

# WIDAR Correlator Board Component Software

Kevin Ryan National Radio Astronomy Observatory

## WIDAR board component software

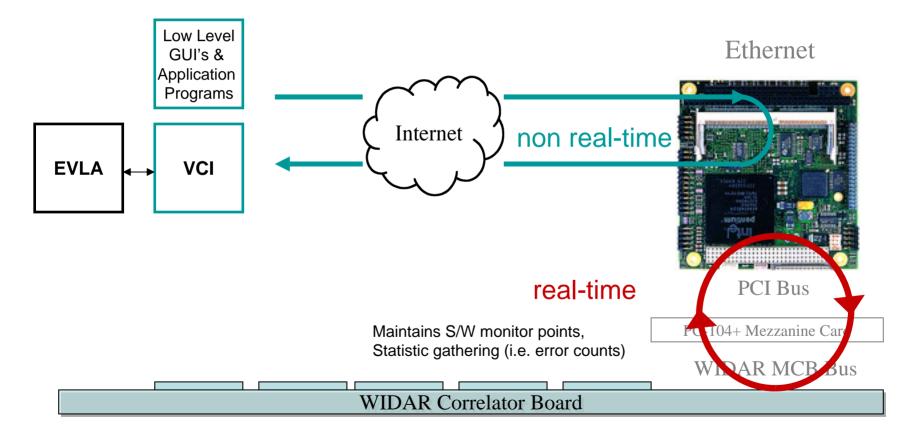

Normal operation of the WIDAR Correlator in the EVLA will be done through the Virtual Correlator Interface (VCI).

During the installation and initial phases of operation however, some of the control, monitor and testing will be done at lower, board and individual component levels.

The purpose of this discussion is not for the review of the design of the board-level software but for review of its interface for initial integration of WIDAR into the EVLA system.

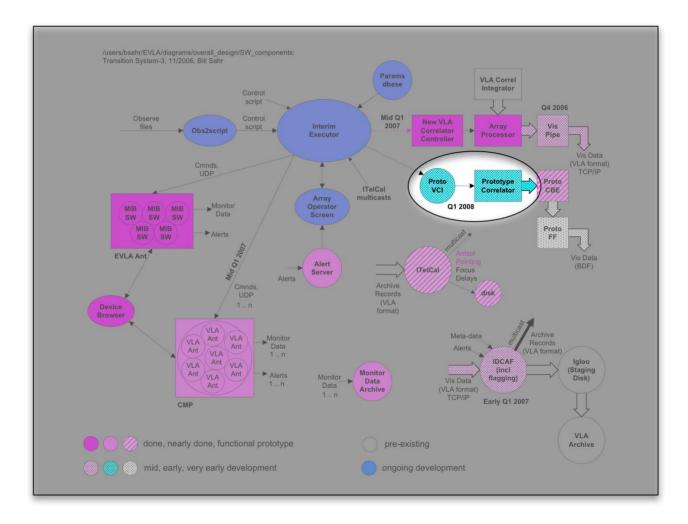

### Place in the System

### EVLA M&C Transition S/W CDR Dec 5-6, 2006

# **Discussion Content**

- Overview of Correlator (Physical Description)

- S/W Requirements References

- Network 'Middleware'

- CMIB (Server-side) Software

- GUI (Client-side) Software

### **WIDAR Physical Description**

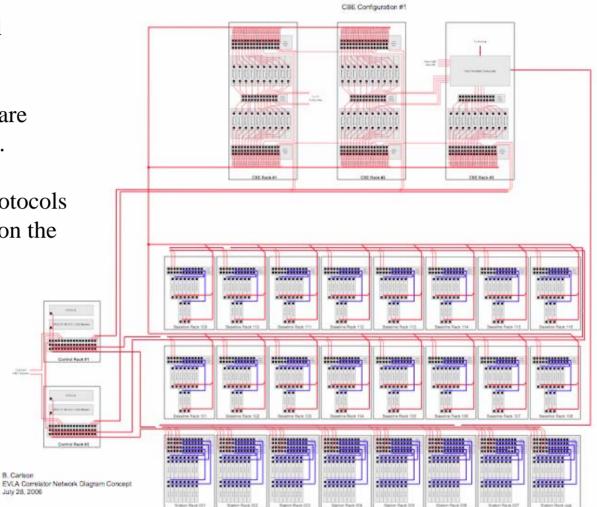

Racks in the WIDAR System:

- 2 Control Racks (one is hot standby) each:

- 2 CPCCs (Correlator Power Control Computers)

- 3 CMIB Boot Servers

- MCCC functionality may reside on one of these

- 3 CBE Racks

- Containing  $\approx$  50 Blade Servers

- 24 Correlator Racks

- Contain the correlator electronics

- The boards of interest for this discussion are the Station and Baseline boards.

### A 32-station correlator:

| 24 Correlator Racks | 5 | Boards per Rack |                     |

|---------------------|---|-----------------|---------------------|

| • 16 Baseline       | Y | • 10            | 160 Baseline Boards |

| • 8 Station         | Λ | • 16 -          | 128 Station Boards  |

|                     |   |                 |                     |

EVLA M&C Transition S/W CDR Dec 5-6, 2006

Each board contains dozens of configurable devices • Correlator Chips, FIR Filter FPGA's, Recirculator FPGA's, LTA FPGAs, etc.

| Boards       |   | Devices/board |   | <b>Total Devices</b> |

|--------------|---|---------------|---|----------------------|

| 160 Baseline | V | 146           |   | 23360                |

| 128 Station  | Λ | 47            | = | 6016                 |

## $\approx$ 30,000 devices to be configured/monitored

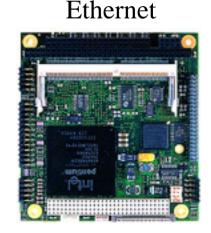

Each Station and Baseline board contains a PC-104 computer

- Correlator Module Interface Board (CMIB)

- 166-MHz Intel Pentium processor

- Linux OS

- >= 128 Mbytes RAM

- no disk or FLASH

- 100 Mbit Ethernet

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

# S/W Requirements

## WIDAR Board S/W Requirements

### The WIDAR document site:

http://www.drao-ofr.hia-iha.nrc-cnrc.gc.ca/science/widar/private

- General CMIB and UI performance:

- RFS\* Document A25204N0001, "Software Requirements for Testing of the Board Prototypes", Sonja Vrcic, Bruce Rowen.

- TVP\*\* A25081N0001, Baseline Board Prototypes, B. Carlson

- TVP A25040N0003, Station Board Test and Verification Plan, D. Fort

- RFS A25220N0000 Prototype Board User Interface Description, K. Ryan

- User Manual A25200N0011, Programmer's Guide to the EVLA Correlator User Interface System, K. Ryan

- Specific Requirements for S/W-H/W interaction:

- User Manual A25290N0000, Programmer's Guide to Correlator System Timing, Synchronization, Data Products, and Operation

- Various other RFS documents, one for each of the FPGA's and Correlator Chips

\*Requirements and Functional Specification \*\*Test and Verification Plan

### WIDAR Board S/W Requirements (cont.)

## Very generally:

- CMIB S/W

- Provide board initialization

- Load FPGA personalities

- Perform constant real-time monitor/control of board hardware

- Provide specific board 'functionality'

- Provide an interface to that functionality for external applications

- User Interface S/W

- Provide various levels of access to hardware

- Whole board configuration

- Individual device (FPGA, Correlator Chip) configuration

- Peeking/poking individual registers within a device

# **Communication Middleware**

## **Middleware Description**

- Every computer, even embedded, is connected via IP/Ethernet.

- COTS network hardware

- switches, cabling.

- All communication protocols are the same ones used on the Internet.

A natural middleware candidate for this type of infrastructure is one based on the Internet and, more specifically, the World Wide Web.

REST (Representational State Transfer) is an architectural style created to describe the World Wide Web

"REST provides a set of architectural constraints that, when applied as a whole, emphasizes scalability of component interactions, **generality of interfaces**, [and] independent deployment of components."

R. Fielding, <u>Architectural Styles and the Design of Network-based Software Architectures</u>, PhD. Disertation, University of California, Irvine, 2000.

### REST is Client/Server based In WIDAR:

- Servers are the remote computers and processes representing the system that is to be M&C'd.

- CMIBs are the servers of correlator board/chip-level M&C.

- Every WIDAR server (including CMIBs) will have a Web Site.

- Clients are the UI's and other M&C'ing applications

- Client s/w can be hosted on any machine connected to the Internet.

- UI's can be specially created GUIs or standard Web browsers.

# The WIDAR Correlator will sport almost 300 individual Web sites.

"REST components perform actions on a resource by using a representation to capture the current or intended state of that resource and transferring that representation between components."

In WIDAR, resources are:

- Hardware

- a chip, a board, a register, the whole correlator

- Data

- configuration files, correlator data files

- streaming data

Fielding

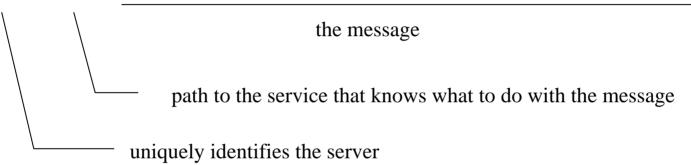

REST uses two well-defined industry standards to communicate these resource representations between client and server:

- The URI to specify the resource

- (the URL is a subset of the URI)

- HTTP to transport its representation

In a manner opposite of RPC architectures, REST is

- "resource-centric rather than method-centric".

- "it defines a small global set of verbs (the HTTP Methods: GET, POST, PUT, etc) and applies them to a potentially infinite set of nouns (URIs)."

P.James, http://www.peej.co.uk/articles/rest.html

WIDAR hardware representations are conveyed in XML

- It describes the *state* of the component

- configuration parameters, error counts, statistical counts, register values

### M & C of WIDAR consists of communicating XML messages of current and intended states between its components.

An XML message can be simple:

<lta id='x1y2'><state register=''/></lta>

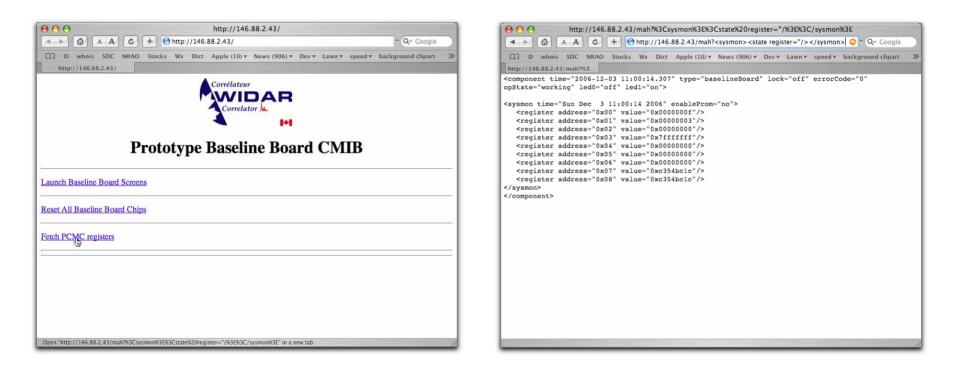

### The XML can be placed inside a URL and sent via HTTP GET:

http://cmib1/mah?<lta id='x1y2'><state register=''/></lta>

• The URL above is what a GUI sends to a CMIB to retrieve the values of an LTA's register set.

• It can also be entered into a standard web browser (or clicked on as a link) to display the registers ...

### An HTML link to fetch the PCMC's register set:

<a href="mah?<sysmon><state register=''/></sysmon>">Fetch PCMC registers</a>

XML is also stored in *configuration files*.

# GUIs can read and write the files and ...

| 😝 😝 Prototyp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e BaseLine Board Recirculator FPGA Y2                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reen FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | Screen Not Locker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Arrow         Total         Total         Total         Total           B0         50         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |                                                                                        | Screen Net Lecter           UnimeCode           UnimeCode |

| WIDAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ractor<br>Blocksize<br>Santlock 255<br>Enetlock 255<br>Tetallioks 228<br>Recirculation | Redisal - OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

... GUIs can read and write XML back and forth to hardware

| 000                                                                                                                                                                                                                         | Untitled 4.txt                                                                                                                    |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|

| aboseline time."The Jon 18 18:15:19 28                                                                                                                                                                                      | 5°>                                                                                                                               |          |

|                                                                                                                                                                                                                             | 19 2006" id="x0" blockSize="256" blockSizet="1" blockEnd="255" blockTotal="120" dampStation="X" activate="enable"                 |          |

| inputDecode+"disple"                                                                                                                                                                                                        | tacCodeCources'dated 1" timeCodes'2007.213.11.23.25.030" outputPates'250H" heLociTrables'on' nuRecircStreams'1"                   |          |

| stfCount+"654321" trig                                                                                                                                                                                                      | dfrrCant.*1234%*>                                                                                                                 |          |

| sinternalStreamConfig id="@" stati                                                                                                                                                                                          | mid="110" subBandid="10" baseBandid="0" inputStressid="7" outputSource="recirculator" sampleRate="640" sampleSize="46" ribble="   | 1.587.0- |

| sinternalStreamConfig id="1" stati                                                                                                                                                                                          | nid-"111" subBandid-"11" baseBandid-"1" insuffiremid-"7" substitutiource-"recirculator" sampleRate-"1200" sampleFire-"7b" nibble- | ***** () |

| sinternalStreamConfig id="2" stati                                                                                                                                                                                          | mide"112" mbBandide"12" baseBandide"2" inputStreamide"5" outputSourcee"recirculator" samplePatee"2564" sampleFiree"46" nitble-    | -LSN /2  |

| <internalstreamconfig id="3" stati<="" td=""><td>nid-"113" subBandid-"13" baseBandid-"3" inputStreamid-"4" outputSource-"recirculator" samplePate-"5120" sampleSize-"76" mibble-</td><td>TEN'/s</td></internalstreamconfig> | nid-"113" subBandid-"13" baseBandid-"3" inputStreamid-"4" outputSource-"recirculator" samplePate-"5120" sampleSize-"76" mibble-   | TEN'/s   |

| <internalstreamconfig id="4" statt<="" td=""><td>nid-"114" n#Bandid-"14" bateBandid-"4" inputStreamid-"3" outputSource-"internal" samplePate-"1N" sampleSize-"4b" nibble-"LSN"/</td><td>2</td></internalstreamconfig>       | nid-"114" n#Bandid-"14" bateBandid-"4" inputStreamid-"3" outputSource-"internal" samplePate-"1N" sampleSize-"4b" nibble-"LSN"/    | 2        |

| <internalstreamconfig id="5" stati<="" td=""><td>nid="115" subBandid="15" baseBandid="5" inputStressid="2" suppriSource="internal" suppleStre="26" suppleStre="76" nibble="76"</td><td>~</td></internalstreamconfig>        | nid="115" subBandid="15" baseBandid="5" inputStressid="2" suppriSource="internal" suppleStre="26" suppleStre="76" nibble="76"     | ~        |

| <internalstreamconfig id="6" statt<="" td=""><td>nld="116" subBandid="16" baseBandid="6" insutStressid="1" superSource="internal" suppleSurce="48" suppleSize="46" nibble="158"/</td><td>6</td></internalstreamconfig>      | nld="116" subBandid="16" baseBandid="6" insutStressid="1" superSource="internal" suppleSurce="48" suppleSize="46" nibble="158"/   | 6        |

| sinternalStreamConfig id="7" statt                                                                                                                                                                                          | nid-"117" pubBandid-"17" bateBandid-"7" inputStreamid-"0" outputSource-"internal" samplePate-"60" sampleSize-"7b" nibble-"60"     | 6        |

| -rectrostreasConftg td-"0" interna                                                                                                                                                                                          |                                                                                                                                   |          |

| <rectrostreamconftg interna<="" td="" tdw"1"=""><td>31recald="0" povioad="phase"/&gt;</td><td></td></rectrostreamconftg>                                                                                                    | 31recald="0" povioad="phase"/>                                                                                                    |          |

| -greatrastreasConfig id="2" interna                                                                                                                                                                                         |                                                                                                                                   |          |

| -rectrostreaconfta td+"3" interna                                                                                                                                                                                           | 3tread4-11 payload-"phase"/>                                                                                                      |          |

| -precircStreamConfig id+"4" interna                                                                                                                                                                                         | StremId="4" pgyload="data"/>                                                                                                      |          |

| -greatraitreanConfta ta+"5" interna                                                                                                                                                                                         | StreenId='5' pov/ood='data'/>                                                                                                     |          |

| <pre>crecircStreamConfig td+"6" interna</pre>                                                                                                                                                                               | StreamId="6" payload="data"/>                                                                                                     |          |

| -rectroStreamConftg td+"?" Interna                                                                                                                                                                                          | 3treadd="7" poyload="data"/>                                                                                                      |          |

| -dest forceStreamane+"0UPP_SYNC"                                                                                                                                                                                            | arceStreamLine="7" forceStreamBit="3" forceBitValue="normal" testVector="off"/>                                                   |          |

| -telecetver standtid="datad" crcEr                                                                                                                                                                                          | ars-"d" offsetErrors-"d" toggle-"true" accurine-"1234567" phaseHodCount-"d" dupCount-"d" lockStatus-"locked" />                   |          |

| <pre>-telecetver standtId="data1" crcEr</pre>                                                                                                                                                                               | ars-"1" offsetErrors-"1" toggle-"true" accurTime-"123567" phasefladCount-"1" dupCount-"1" lockStatus-"locked" />                  |          |

| -reflecetver signatid="data2" crcEr                                                                                                                                                                                         | ars+"22" offsetErrors+"22" toggle+"true" accurTime+"1294567" phasefladCount+"22" dumpCount+"22" lockStatus+"locked" />            |          |

| -refleceiver standtid="data3" crcEr                                                                                                                                                                                         | ars-1333" offsetErrors-1333" toggle-"true" accumTime-1234567" phaseflodCount-1333" duepCount-1333" juckStatus-Tipoked" />         |          |

|                                                                                                                                                                                                                             | ors-"++++" offsetErrors-"++++" togle-"true" accur[ie="129557" phasehotCount="++++" dueCount="++++" jockStatus="jocked" />         |          |

| defectiver standild+"data5" crcEr                                                                                                                                                                                           | ars-"55555" offsetErrors-"55555" toggle-"true" accurline-"1294567" phaseflad.ourt-"55555" dueCourt-"55555" jociStatus-"rotipoke   | et 15    |

| defectiver standild, data6" crcEr                                                                                                                                                                                           | ars-"666666" offsetErrors-"666666" toggle-"true" accumTime-"1234567" phosefodCount-"666666" dumpCount-"666666" (poiStatus-"1ppk   | 100 12   |

|                                                                                                                                                                                                                             | ors-"7777777" offsetErrors-"777777" togie-"foise" acum[ime-1234567" photehol(ourt-"77777" amelourt-"77777" ipchStatus-"ip         |          |

| defectiver standtIde"timeCode" or                                                                                                                                                                                           | Errors-'1' offsetErrors-'1294567' togle-'true' occurine-'1294567' />                                                              |          |

|                                                                                                                                                                                                                             | Errors-12" offsetErrors-120456" toggle-"true" accurTime="1204567" />                                                              |          |

| defleceiver standilde"shasehod" or                                                                                                                                                                                          | Errors-123" offsetErrors-12345" toggle-"true" accurTine="1234567" />                                                              |          |

|                                                                                                                                                                                                                             | crcErrors-"1204" offsetErrors-"1204" toggle-"true" occurTine-"1204567" />                                                         |          |

| defleceiver standild="phaseErr2_3"                                                                                                                                                                                          | crcErrors="12045" offsetErrors="120" toggle="true" occurTime="1204567" /s                                                         |          |

| defleceiver standilde"phaseErr4.5"                                                                                                                                                                                          | crcErrors="120456" offsetErrors="12" toggle="true" occueTise="1204567" /s                                                         |          |

| -tweeceiver signalId="phaseErr6_7"                                                                                                                                                                                          | crcErrors-"1204567" offsetErrors-"1" toggle-"true" occurTine-"1204567" />                                                         |          |

| about fpgdierston="14" fpgdievtst                                                                                                                                                                                           | n="8" driverVersion="version 0.1"                                                                                                 |          |

| status="ck" functionType="@                                                                                                                                                                                                 | 2.                                                                                                                                |          |

| k/recirculators                                                                                                                                                                                                             |                                                                                                                                   |          |

|                                                                                                                                                                                                                             |                                                                                                                                   |          |

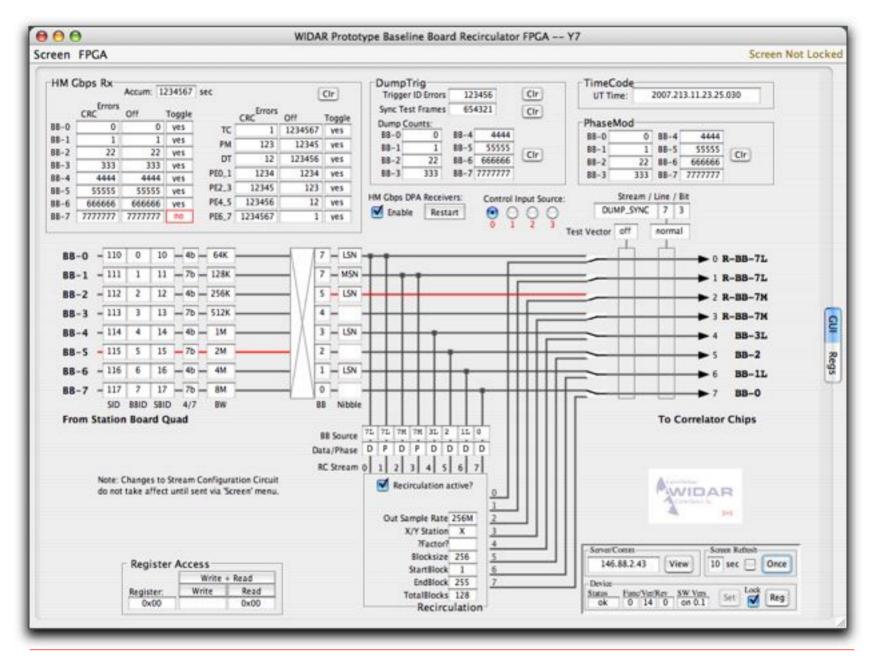

- once loaded they provide a graphical representation of the XML *in the context of the hardware*

- the settings can be modified in the GUI (pressing buttons, etc.) and sent back to the file or to the hardware itself.

Recirculator FPGA

## Configuration files reside on the servers

This allows loading them by communicating only their name over the network rather than sending the whole file.

Board-level GUIs provide means to load configuration files into all of a board's devices in one operation.

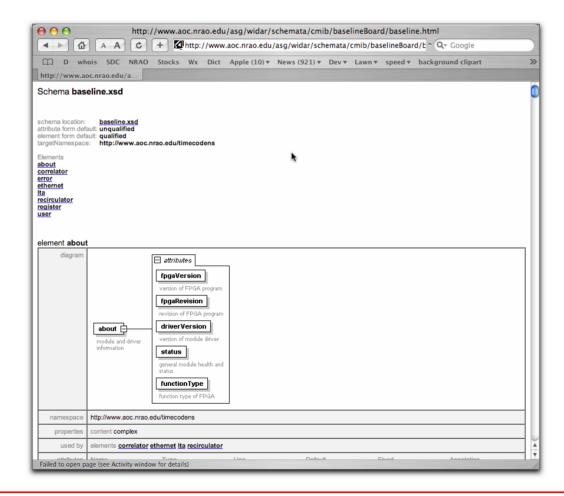

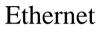

### Each WIDAR component 'API' is defined by XML schemata

- At: http://www.aoc.nrao.edu/asg/widar/schemata/

# **CMIB** Software

Bruce Rowen / Kevin Ryan

### **CMIB** Software Description

CMIBs maintain constant real-time control of their attached board and provide an on-demand, non-real-time interface to external users.

- Off the shelf Linux.

- At boot time, a file system is mounted (via NFS) from one of the CMIB server machines.

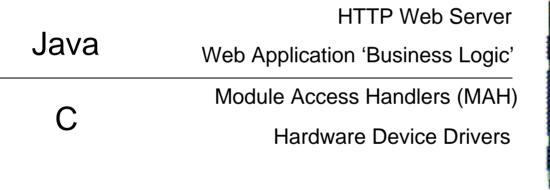

- Layers of application software:

Ethernet

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

Server-side external interface software

• Apache's Tomcat off-the-shelf web server

### HTTP Web Server

Web Application 'Business Logic'

Module Access Handlers (MAH)

Hardware Device Drivers

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

Server-side external interface software

- Web-based interface to client applications

- Device Driver like interface to MAHs (similar to file or Unix pipe I/O)

- Java Servlets and JSPs

- Web site (static web pages)

HTTP Web Server

### Web Application 'Business Logic'

Module Access Handlers (MAH)

Hardware Device Drivers

Ethernet

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

### MAHs run in Linux User space

- XML interface to next higher level

- Translates XML to IOCTL calls

- Provides three levels of h/w access:

- Register (I/O directly with an FPGA/Correlator Chip)

- Basic Function (mnemonic access to FPGA functions)

- Abstract Function (generic configuration and control, hides FPGA structure)

HTTP Web Server

Web Application 'Business Logic'

Module Access Handlers (MAH)

Hardware Device Drivers

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

Real-time software that runs in Linux Kernal space

- 10 millisecond interrupts

- IOCTL interface to MAH layer

- Memory mapped I/O to h/w via PCI bus

- Provides low-level control/monitor

- 'software' monitor points

### HTTP Web Server

Web Application 'Business Logic'

Module Access Handlers (MAH)

Hardware Device Drivers

PCI Bus

PC-104+ Mezzanine Card

WIDAR MCB Bus

# **Board-Level GUIs**

Sonja Vrcic / Kevin Ryan

## **GUI** Software Description

## GUI's:

- Operate on Windows, U/Linux and Mac OS-X,

- Operate over the Internet,

- We are currently using them for initial debug and test of the recently arrived prototype Baseline Board in Penticton, BC, Canada.

- Are created using Java's Swing components,

- Are served to clients from AOC's Web Server,

- Are launched using Java Web Start.

- A user simply points his browser to a CMIB's web site and clicks on the application's link.

- This assures that the client is using the most up-to-date version.

- If the client has the latest version, no downloading is necessary.

Software common to GUIs such as reusable sub-panels, XML parsing and HTTP communication, are packaged separately and their API documented on a web site with Javadoc.

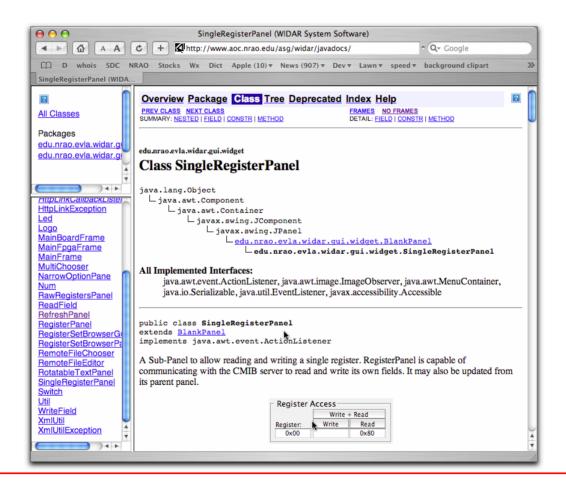

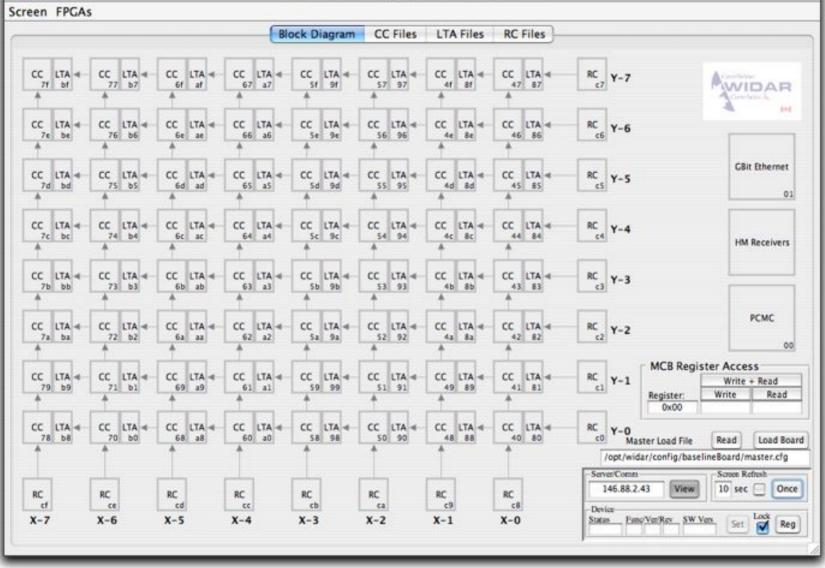

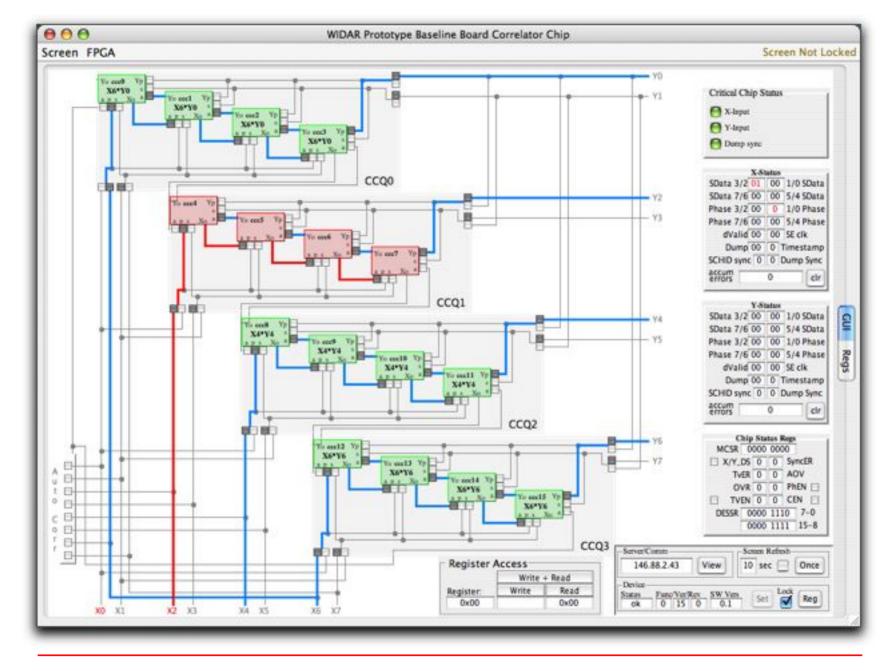

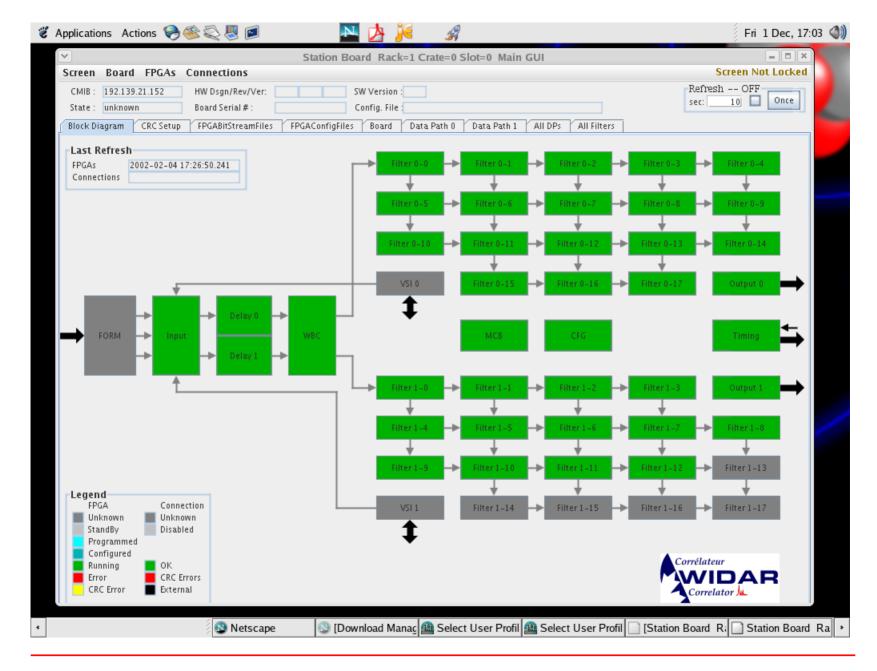

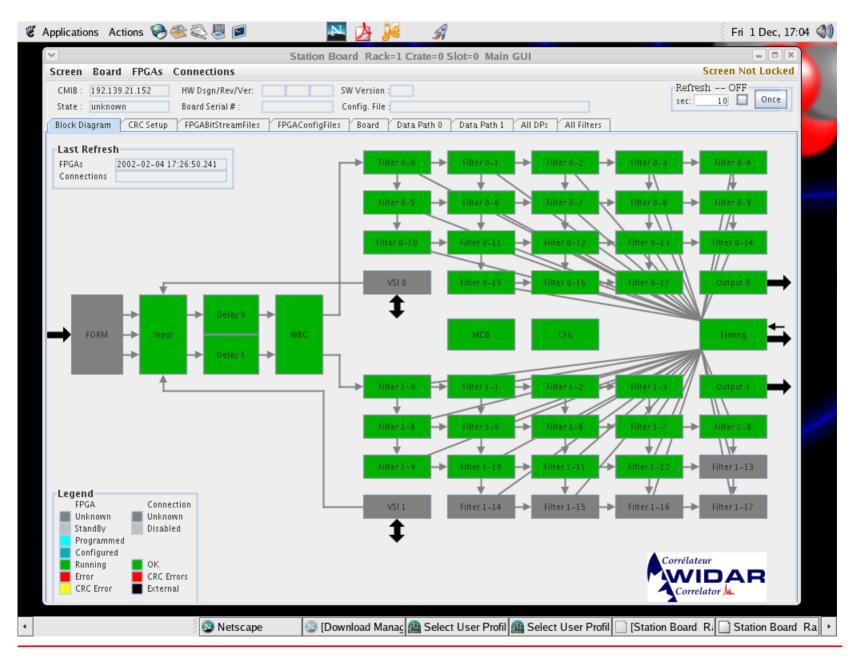

Station Board and Baseline Board GUIs:

- Consist of an overall board block diagram,

- Depicting its various sub-components (referred to as 'devices' or simply 'chips').

- and at least one chip-level GUI for each of the board's sub-components.

- That show the 'inside' of the device,

- Are launched by clicking on the chip's icon on the board block diagram GUI,

- Provide at least one panel showing the device graphically and also a panel providing lower-level access to the device's register set.

Engineers in Penticton provided detailed diagrams and functional requirements/specifications for the GUIs.

As the prototype boards are undergoing initial testing, the GUIs are also thoroughly being 'wrung-out' for correctness and for modification as necessary.

#### Prototype Baseline Board test -- 20061201-1531

### 000

#### WIDAR Prototype Baseline Board Long Term Accumulator FPGA

Screen Not Locked

Screen FPGA

### EVLA M&C Transition S/W CDR Dec 5-6, 2006

| Applications Actions 🛞 🎕 🔍 📧 🛛 🔤 🙀 🎉                                                                                                                                                                                                                                                                               | 🖗 Fri 1 Dec, 17:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Station Board Rack=1 Crate=0 Slot=                                                                                                                                                                                                                                                                                 | =0 FILTER 0-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| creen FPGA                                                                                                                                                                                                                                                                                                         | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| creen       FPGA         Common       sate:       ok         sate:       ok       Last refresh:       Mon Feb 4 17:36:40 2002         VW Version:       0.1       FPGA D/R/V:       108       6       5         onfig. File:                                                                                       | InOut<br>Input: 0 Enable Output: 0 1 Output # bits: 4<br>I/O Buffer Delay: 192 Daisy Delay: 1701519410<br>Time Interval: Cfg register: 0X0004<br>Delay<br>Divider: 4 Specify Delay Model via GUI<br>Demux Factor: 0 Free running mode<br>Phase Factor: 0 Delay: 0<br>Delay Rate: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| aput # bits:     3     Output # bits:     4     Mixer:       aput # bands:     1     Tone frequency (Hz):     0     MPEC:       aput band:     0     Delay module delay rate:     10.0     LSB:       Specify Models via GUI     Tick Delay:     0     0       elay:     0.0     Signal dominated input:     Setup | Stage1         Product File:       Browse         Output Divider:       0         Invalid Stretch:       0         Scale Factor:       0         Number of Taps:       512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ormat<br>lect Data: stage1 Power: on off<br>Valids: on off<br>lect Clip: stage3 Clip Count:                                                                                                                                                                                                                        | Mixer Trig File:     Iut/mixtab.lut     Browse       Use mixer     Specify Mixer Model via GUI     Phase:     0       Use MPEC     Free running mode     Phase Rate:     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FI Detect Level: 0 RFI Detections:<br>FI Invalid Stretch: 0<br>deband Flipper: 0 On<br>uantizer Scaling: 0 Quantizer Power: 0<br>uantizer # Bits: 5 Quantizer Clip Count: 1<br>uantized State: Auto 244 Quantizer Scale Count: Histogram                                                                           | Stage2         Coefficient File:       Browse         Output Divider:       0 Calculation Divider:       256MHz         Invalid Stretch:       0 Filter Delay:       0         Scale Factor:       0 Number of Taps:       64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| one Extraction (TEX):<br>2X Trig File: Browse Specify TEX Model via GUI Free running mode X Phase: TEX Valids: X Phase Rate: TEX Sums: Cos Sin                                                                                                                                                                     | Stage3         Coefficient File:       Browse         Output Divider:       Error 256KHz Calculation Divider:       256MHz         Invalid Stretch:       29500 Filter Delay:       15919         Scale Factor:       60 Number of Taps:       _UNKNOWN_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Status     CRC       FIR32[00]     0     FIR32[08]     0       FIR32[01]     0     FIR32[09]     0       FIR32[02]     0     FIR32[10]     0       FIR32[03]     0     FIR32[11]     0       FIR32[04]     0     FIR32[12]     0       FIR32[04]     0     FIR32[13]     0                                         | Stage4         Coefficient File:       Browse         Output Divider:       rror _UNKNOWN_ Calculation Divider:       256MHz         Invalid Stretch:       0       Filter Delay:       0         Scale Factor:       0       Number of Taps:       64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FIR32[06] 0 FIR32[14] 0 sec: 10 0nce<br>FIR32[07] 0 FIR32[15] 0                                                                                                                                                                                                                                                    | Register Access     Test Port       Write + Read     TP0       TP0     TP1       TP0     TP2       TP0     TP1       TP1     TP2       TP1     TP2 |

### 🐮 Applications Actions 🥪 🥸 🔍 🗾

| Station Board Rack=1 Cr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rate=0 Slot=0 INPUT FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rinput / Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| State:       ok       Last refresh:       Mon Feb 4 17:30:08 2002         S/W Version:       0.1       FPGA D/R/V:       0       0       12         Config. File:       Bit Str. File:       Browse         Log level:       LOG_WARNING       Browse       Browse       Browse         Display FPGA Registers       Display CRC Error Counters       Browse         VCI       Input # bits per sample:       3       3         Data Path 0 Source:       FORM stream0       Data Path 1 Source:       FORM stream1         Noise Diode On/Off       Width:       0       Setup         Rate:       0       Setup       Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Path 0 Source: stream0   Format: 4Bit   Data Path 1 Source: stream0   Translation RAM Block: 0   Test Generator On/Off   Translator Table File:   Collect   Data Path:   0   Histogram   Block Id:   Band   State   Counter   Band   State   Counter   Band   State   Counter   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0 <t< th=""></t<> |

| Input Ports         Reclocking distance         Input Tick         Input Tick to sysTick Count         DCM         PPS         PP10S         PPS           A:         0         100pps         2137943653         Image: Contemportal cont | Noise Diode       DCM status         Image: On/Off       Image: DCM system lock         Image: DCM system lock       Internal memory address: 255         Phase: 2003726965       Rate: 2071792174         Calculated Phase: 2105483365       Refresh OFF sec: 10                                                                                                                                                                                                                                                                                          |

| Write + Read     Test Port       Write + Read     TP0 TP1 TP2 TP3       0x00     0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 🔇 [Netscape] 🛛 🔇 [Download Man                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | naç 🏨 Select User Profil 📄 [Station Board 🛛 R; 📄 [Station Board 🗛 📄 Station Board 🖓                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

R

N.

A 16

### EVLA M&C Transition S/W CDR Dec 5-6, 2006

| <b>ë</b> . | Application                                                                                                  | s Act    | tions   | 0       | S 2     | 2 🛃 🖻                  |                        | N    |           | 为 🎉     | 3        | 9         |              |       |                |      |      |                    |           |         | Fri   | 1 De          | c, 17 | 7:09 🜒 |

|------------|--------------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|------------------------|------------------------|------|-----------|---------|----------|-----------|--------------|-------|----------------|------|------|--------------------|-----------|---------|-------|---------------|-------|--------|

|            | Station Board Rack=1 Crate=0 Slot=0 Main GUI                                                                 |          |         |         |         |                        |                        |      |           |         |          |           |              |       |                |      |      |                    |           |         |       |               |       |        |

|            | Screen Board FPGAs Connections Screen Not Locked                                                             |          |         |         |         |                        |                        |      |           |         |          |           |              |       |                |      |      |                    |           |         |       |               |       |        |

|            | CMIB: 192.139.21.152 HW Dsgn/Rev/Ver: SW Version:                                                            |          |         |         |         |                        |                        |      |           |         |          |           |              |       | _              |      |      |                    |           |         |       |               |       |        |

|            |                                                                                                              |          |         |         |         |                        |                        |      |           |         |          |           |              | sec   | sec: 10 🔲 Once |      |      |                    |           |         |       |               |       |        |

|            | Block Diagram CRC Setup FPGABitStreamFiles FPGAConfigFiles Board Data Path 0 Data Path 1 All DPs All Filters |          |         |         |         |                        |                        |      |           |         |          |           |              |       | -              |      |      |                    |           |         |       |               |       |        |

|            | Filter Output BLB_IP_Address Side Input Stream                                                               |          |         |         |         |                        |                        |      |           |         |          |           |              |       |                |      |      |                    |           |         |       |               |       |        |

|            | Source of                                                                                                    | input da | ata:    | FORM    | strea   |                        | pecify Model via       | GUI  |           |         |          |           |              |       | 0              |      |      | 146.88.            |           |         |       | 0             |       |        |

|            | Station IE                                                                                                   |          |         |         |         |                        | lay:<br>lay rate:      |      |           | 0.1     |          |           |              |       | 1              |      |      | 146.88.            |           | _       | _     | 0             |       |        |

|            | Baseband                                                                                                     |          |         |         |         |                        | ,                      |      |           | _       |          |           |              |       | 2              |      | 2    | 146.88.<br>146.88. |           |         | _     | 0             |       |        |

|            | Input#bi<br>Input#ba                                                                                         |          |         |         | Ŧ       |                        | ng Mode:<br>Ise width: | 0ff  |           | 10      |          |           |              |       | 4              |      | 4    | 146.88.            |           |         |       | 0             |       |        |

|            | Input # Da                                                                                                   |          | /11-11- |         | 480000  | D                      | lse period :           |      |           | 20      |          |           |              |       | 5              |      | 5    | 146.88.            |           | 1       |       | 0             | 1     |        |

|            | Baseband                                                                                                     |          |         |         | 480000  |                        | equency:               |      |           | 30      |          |           |              |       | 6              |      | 6    | 146.88.            |           | _       | _     | 0             |       |        |

|            |                                                                                                              |          |         |         |         |                        | spersion :             |      |           | 40      |          |           |              |       | 7              |      | 7    | 146.88.            |           | _       | _     | 0             |       |        |

|            | Tone extr                                                                                                    | action ( | Hz):    |         | 10000   | 00] Inv                | /. duration :          |      |           | 50      |          |           |              |       | 8              |      | 8    | 146.88.<br>146.88. |           | _       | _     | 0             |       |        |

|            | RDR outpu                                                                                                    | ut file: | /rdrO   | utFile  |         |                        |                        |      | Brov      | vse     |          |           |              |       | 10             |      | .0   | 146.88.            |           |         | _     | 0             |       |        |

|            | Action: E                                                                                                    | VLA: Se  | t def   | ault E\ | /LA cor | figuration.            |                        |      | Ad        | t       |          |           |              |       | 11             | 1    | 1    | 146.88.            |           | 1       |       | 0             | 1     |        |

|            | _                                                                                                            |          |         |         |         |                        |                        |      |           |         |          |           |              |       | 12             |      |      | 146.88.            |           |         | _     | 0             |       |        |

|            |                                                                                                              |          |         |         |         |                        |                        |      |           |         |          |           |              |       | 13             |      |      | 146.88.            |           |         | _     | 0             |       |        |

|            |                                                                                                              |          |         |         |         |                        |                        |      |           |         |          |           |              |       | 14<br>15       |      | .4   | 146.88.<br>146.88. |           |         | _     | 0             |       |        |

|            |                                                                                                              |          |         |         |         |                        |                        |      |           |         |          |           |              |       | 15             |      | .6   |                    | known X   |         | _     | 0             | -     |        |

|            | Flt Valid                                                                                                    | I ST     | BB      | SB      | Band    | BandWidth              | CentFreq               | Bits | DM        | Delay   | D1vRate  | TickDelay | Fbit         | Flip  | Mix            |      | -    |                    | _         | e ( TEX |       | toN D         | -     |        |

|            | 0                                                                                                            | 1        | 0       |         |         | 128000000              | 64000000               |      |           |         | 0 0      | 0         |              |       |                |      |      |                    |           | 0       | 0     |               | 100   |        |

|            | 1                                                                                                            | 1        | 0       |         |         | 128000000              | 192000000              |      |           |         | 0 0      | 0         |              |       |                |      |      |                    |           | 0       | 0     | _             | 100   |        |

|            | 2                                                                                                            | 1        | 0       |         |         | 128000000<br>128000000 | 320000000<br>448000000 |      | ╞         |         | 0 0      | 0         | 븜            |       |                |      |      |                    |           | 0       | 0     |               | 100   |        |

|            | 4                                                                                                            | 1        | 0       |         |         | 128000000              | 576000000              |      | 븜         |         | 0 0      | 0         | H            | H     | H              | H    | H    |                    |           | 0       | 0     |               | 100   | 1      |

|            | 5 📝                                                                                                          | 1        | 0       |         |         | 128000000              | 704000000              |      | ŏ         |         | 0 0      | 0         | ŏ            |       |                |      |      |                    |           | 0       | 0     | _             | 100   |        |

|            | 6 🖌                                                                                                          | 1        | 0       | 6       | 0       | 128000000              | 832000000              | 4    |           | (       | 0 0      | 0         |              |       |                |      |      |                    |           | 0       | 0     | 0             | 100   |        |

|            | 7 🗹                                                                                                          | 1        | 0       |         |         | 128000000              | 96000000               |      |           |         | 0 0      | 0         |              |       |                |      |      |                    |           | 0       | 0     | $\rightarrow$ | 100   |        |

|            | 8 🖌                                                                                                          | 1        | 0       |         |         | 128000000<br>128000000 | 1088000000 1216000000  |      | $\square$ |         | 0 0      | 0         | $\mathbf{H}$ |       |                |      |      |                    |           | 0       | 0     | _             | 100   |        |