## **High Speed Digitizers**

**EVLA Advisory Committee Meeting**

### Steven Durand & Mike Revnell

Atacama Large Millimeter/submillimeter Array Expanded Very Large Array Robert C. Byrd Green Bank Telescope Very Long Baseline Array

### **High Speed Digitizer Description**

- 8 GHz Bandwidth per polarization

- Consists of eight digitizers, each with a bandwidth of 2 GHz

- Operates in second Nyquist Zone (2-4 GHz)

- Sample clock rate of 4,096 MHz

- 3-bit output each

- 2 GHz Bandwidth per polarization

- Consists of four digitizers each with a bandwidth of 1 GHz

- Operates in second Nyquist zone (1-2 GHz)

- Sample clock rate 2,048 MHz

- 8-bit output each

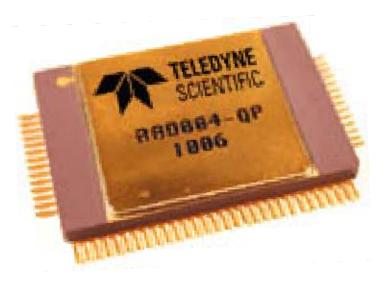

## **Teledyne RAD004**

- Teledyne purchased

Rockwell Scientific including

digitizer division

- Teledyne RAD004

- 6-bit Digitizer

- Bits 0<u>123</u>45

- Analog input bandwidth 12 GHz

- 0.5 Vpp full scale

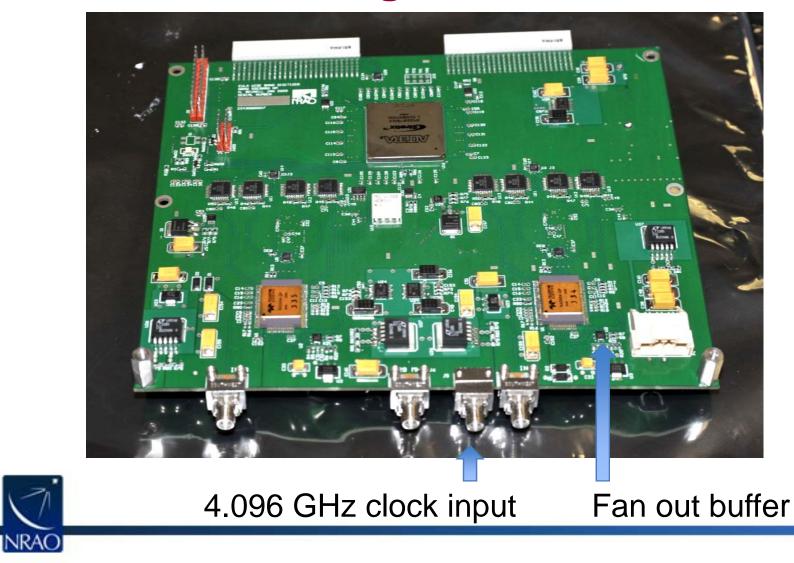

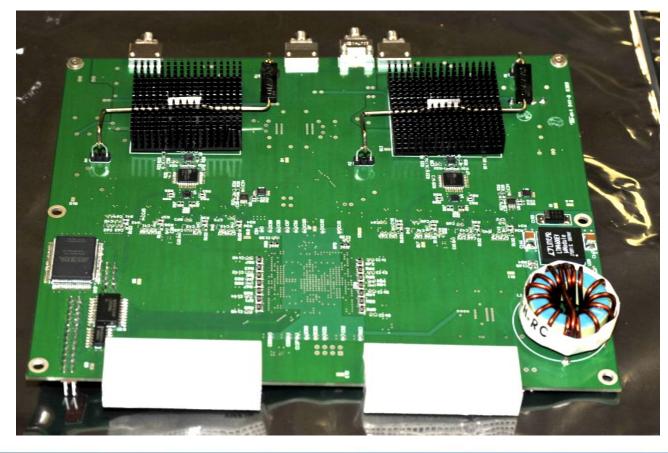

## **3-Bit Digitizer Board**

# 100% Performance testing by Teledyne at Wright Patterson Air Force Base

**EVLA**

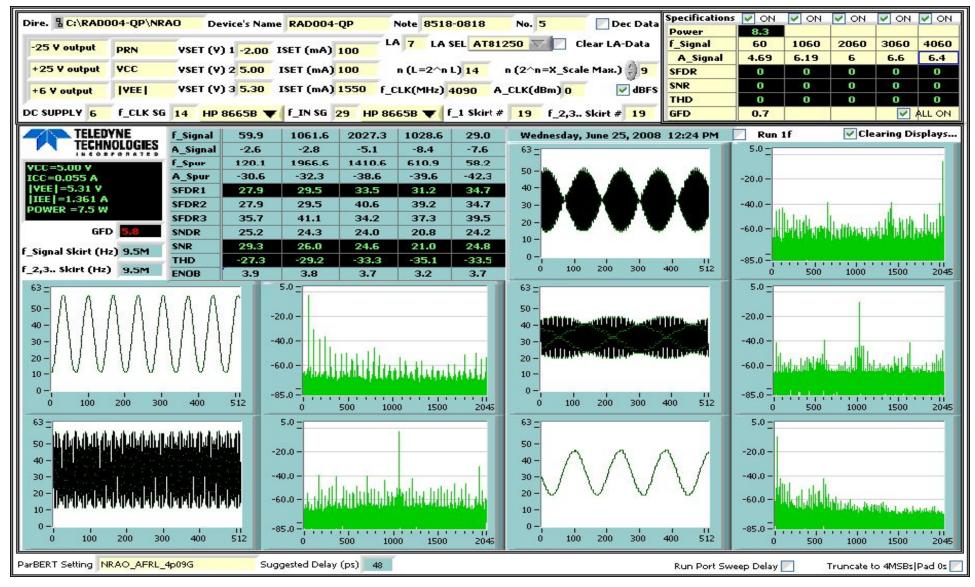

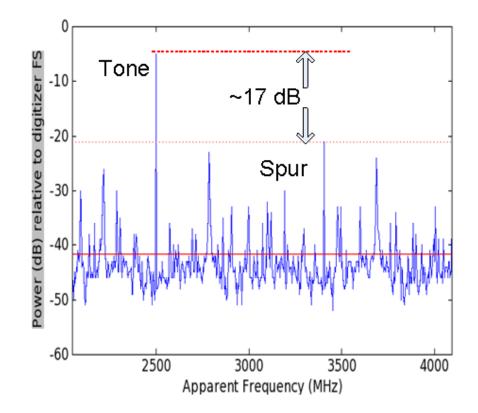

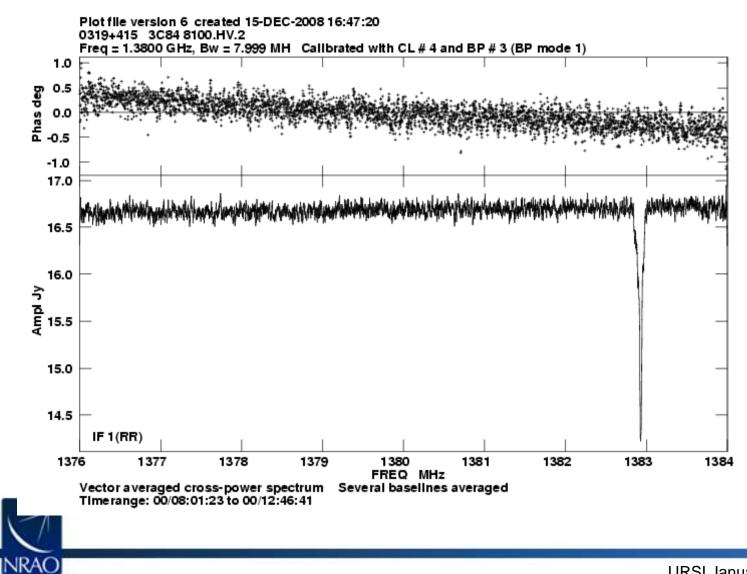

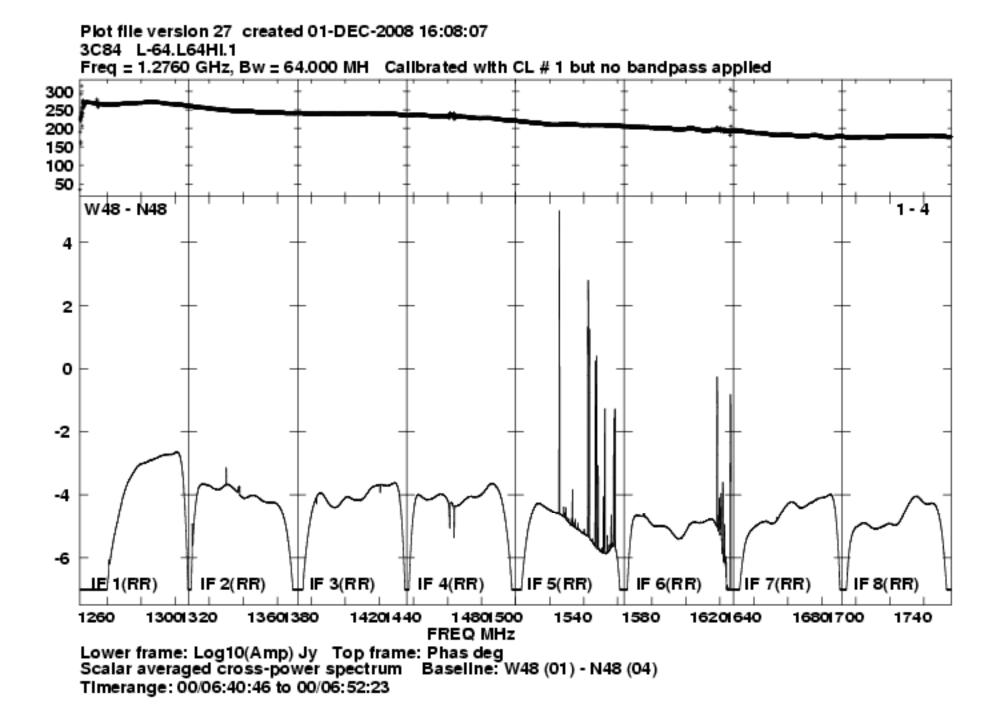

### **Preproduction Board Laboratory tests**

- Spur Free Dynamic Range (SFDR) of ~18dB indicates a successful implementation

- 2048 point FFT

- Data collected in Deformatter board FPGA

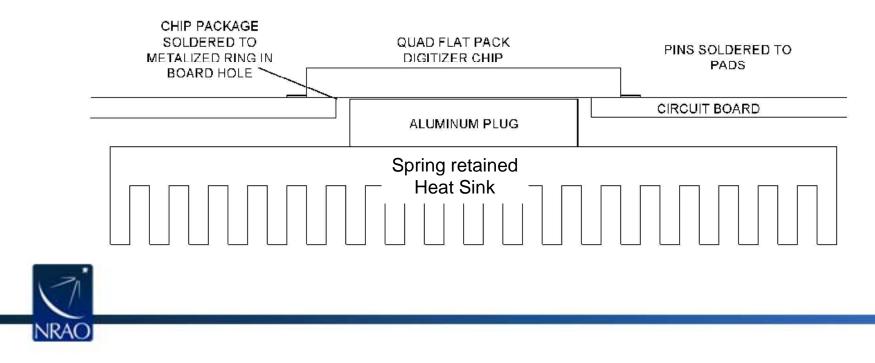

### **3-Bit Digitizer Heat Dissipation**

- 4 GHz clock rate power dissipation ~7.5 W out the back

- Board layout optimized for high speed data performance

- Forced air ventilation and heat sinks provide the cooling

- Temperature sensors will be installed on each heat sink

# Lab bench test indicate the heat sinks provide adequate cooling. Chip case temperature is under 40 C

### Module is designed dissipate 200 W ... present ~80 W

### **Development History**

- Original design (2006) constructed with 2001 date code de-multiplexers

- Prototype passed engineering laboratory tests (2006)

- Decision to proceed with Teledyne based design November 2006

- Contract to purchase Teledyne digitizers awarded in September 2007

- Delivery of digitizers began in September 2008

- Preproduction prototype constructed September 2008 with production parts failed lab tests because of clock rise time problems

- Problem traced to de-multiplexer chips with date code 2006 and 2008

- Modified the design and layout to slow rise times. (Version G)

- Version G is under test

- Scheduled to start installation in the array June 2009

- Plan is to retrofit 18 antennas (8 digitizers each) by July 2010

### **3-bit Digitizer Summary**

- Version G under test

- Installation scheduled to start June 2009

- Farm-out board assembly install in existing DTS modules

- 75% of Teledyne digitizers are in house, remainder by April 2009

- 100% of the digitizers chips tested by manufacturer

- WIDAR verification pending (end-to-end system test)

### **Questions**

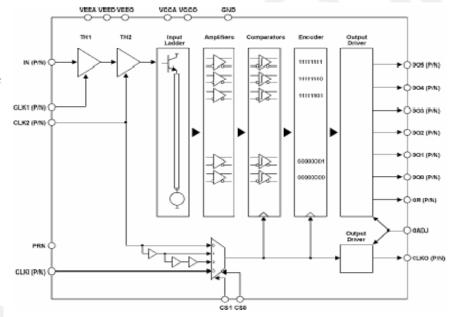

RAD004 DATASHEET – PRELIMINARY DS\_0124XC0-4106

#### 6 Bit 4 GS/s Analog to Digital Converter

#### Features

- 6-Bit Resolution

- Up to 4 GS/s Sampling Rate

- Integrated Dual Track and Hold

- 0.5 Vpp Differential Full Scale Range

- 6 GHz Full Power Bandwidth (min)

- DNL: 0.5 LSB

- INL: 1 LSB

- ENOB: 4.5 Typical (DC to 4 GHz)

- No Missing Codes

- LVDS Compatible, Adjustable CML Output

- Grey Code Output

- Over-Range Indicator Output

- Integrated Pseudo Random Pattern Generator

- 2 Clock Cycles Latency

- 88 Pin QFP Package

- 7.5 W Power Dissipation

- 1 to 4 Demultiplexed Binary Output when Coupled with RDX004M4

- ROHS Compliant

TELEDYNE

SCIENTIFIC COMPANY

EVLA