# The EVLA Correlator P. Dewdney

#### Herzberg Institute of Astrophysics National Research Council Canada

Corrélateur VIDAR Correlator

cil Conseil national de recherches Canada

# Outline

- 1. Correlator Performance Goals

- 2. Hardware Progress

- 3. Software Progress

- 4. System Progress

- 5. Prototype Testing

- 6. Installation Estimates

- 7. Funding, Budget & Schedule

- 8. Risk Issues

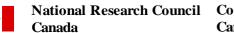

#### Key EVLA Processing Capabilities

National Research CouncilConseil national de recherchesCanadaCanada

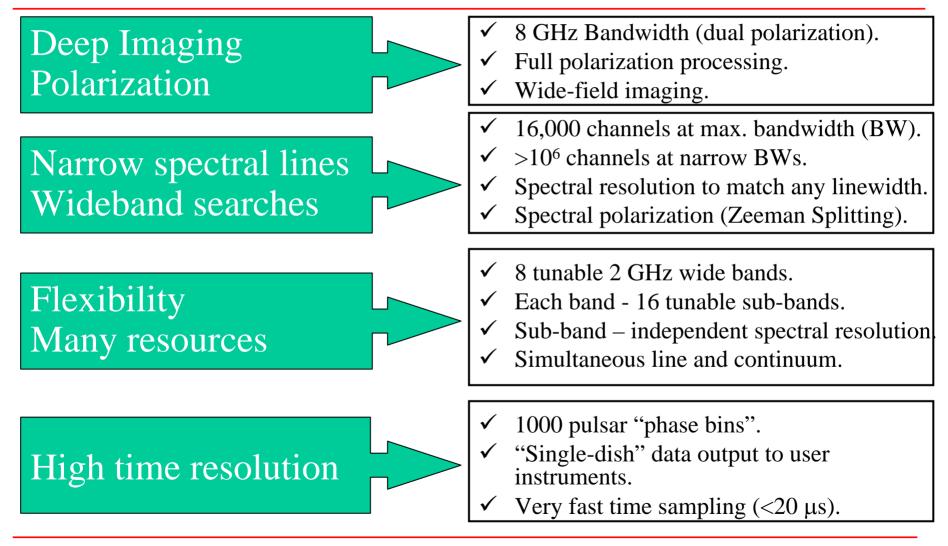

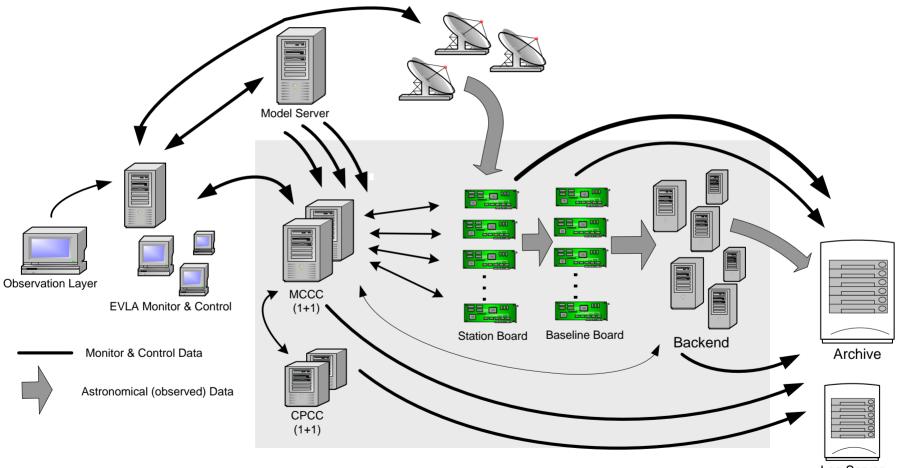

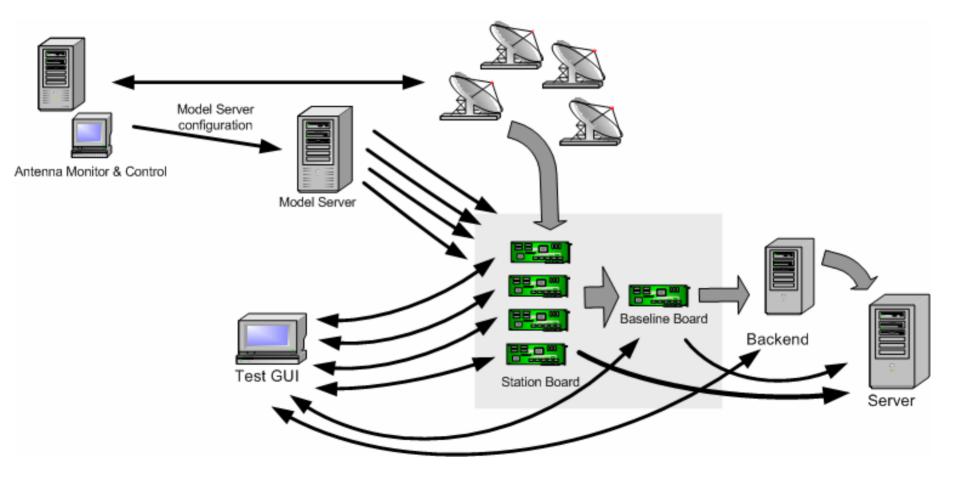

#### **NRC** · **CNRC** EVLA Correlator System Diagram

#### Significant Events Since Dec. 2004

- Correlator Chip CDR Jan/05

- Software Review Jan/05.

- Correlator Preliminary Design Review July/05.

PCB fabricator contract signed Jan/06.

Prototype Correlator chip wafers fab'd Feb/06.

Software Review Mar/06.

Prototype chip delivery early Jun/06.

- Baseline Board prototype delivery Jun/06.

Station Board prototype delivery est. Aug/06.

#### Hardware Progress

- FPGA's

- All FPGA's are designed, including the Filter Chip.

- Station board

- Layout is close to completion, including Design-for-Manufacture approval.

- Presently undergoing signal integrity simulation.

- Prototype fabrication order expected in June.

- Baseline Board

- Prototype fabrication under way.

- Phasing board

- Draft specification (RFS) released.

- Deferred in time but not reduced in priority.

- Other boards

- Prototypes for all other boards already fabricated.

- Fan-out board needs redesign for better signal margins.

- System

- Racks designed and prototyped; thermal analysis done.

- Power system RFP draft written.

- Reliability analysis system in place first draft of analysis complete.

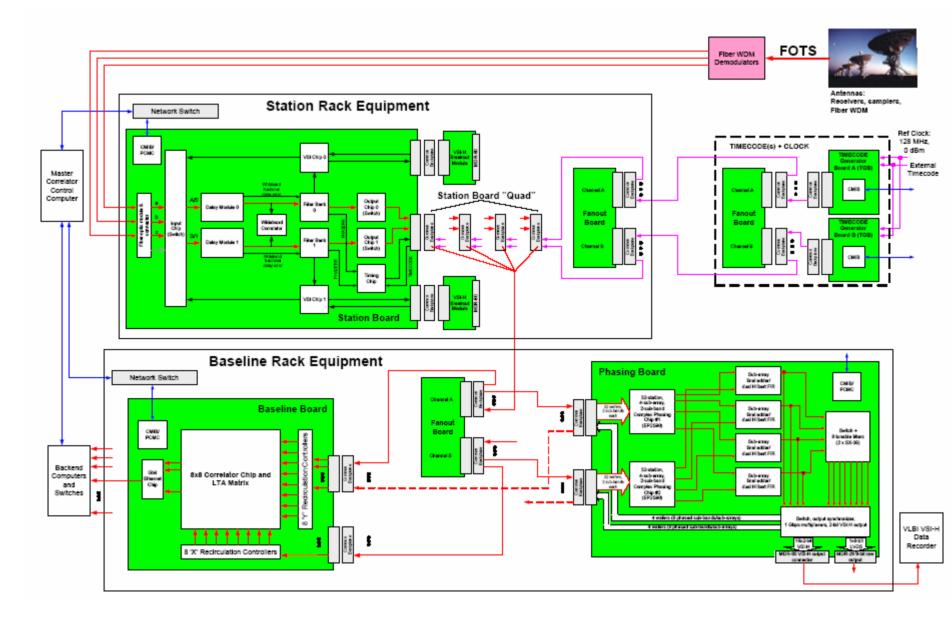

#### **Station Board Layout**

- "Daughter" Board brown.

- Power Supplies pink.

- FPGA's Green

- Connectors light brown and white.

- ~5000 parts.

- 140 required for EVLA.

NRC · CNRC

#### Size: ~510 x ~410 mm

#### **Baseline Board Layout**

- Green chips front side.

- Blue chips back side.

- 8 x 8 array of correlator chips.

- LTA chips on the back side.

- Recirculation Controller.

- ~12000 parts

NRC · CNRC

• ~177 required for EVLA.

# 2.775 1428 92.0 ST 875

#### NRC · CNRC

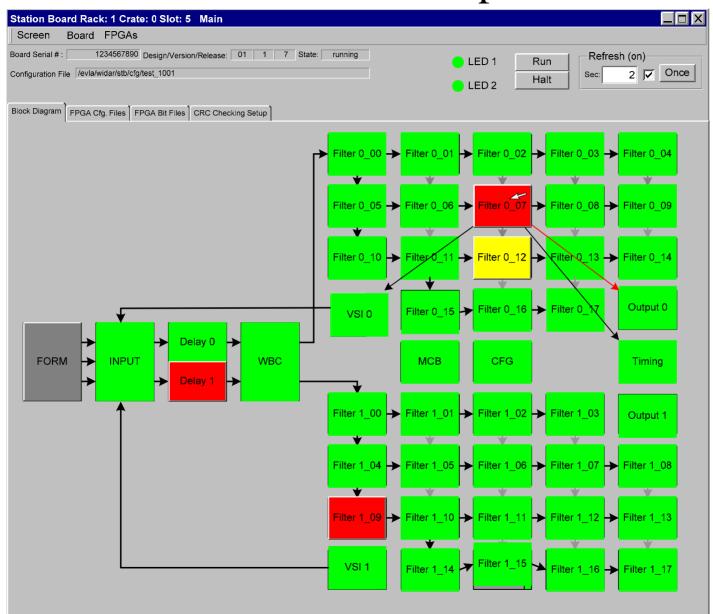

#### Software Progress

- GUI-based prototype testing software

- Complete enough to be useful already.

- All FPGA's covered except Phasing Board.

- **Provides "engineer's view of correlator system.**

- Permanent maintenance value.

- Top-level GUI's now under development.

- Virtual Correlator Interface

- Well defined except for correlator output area.

- Communications protocol well defined except for transport layer.

- Master Correlator Control Computer (MCCC)

- Work deferred for GUI development.

- Architecture/scope well defined.

- Real-time control software

- "CMIB" processor on each board.

- Operating system has been working for a long time.

- XML-based communication with "outside world".

- Drivers for FPGA's are well under way.

#### Correlator Software System Context

Log Server

####

Main

#### Correlator System GUI

#### WIDAR Correlator - Top level system view (40 stations configuration)

####

| Iviani           |                   |                   |                  |                           |

|------------------|-------------------|-------------------|------------------|---------------------------|

|                  |                   |                   |                  |                           |

| MCCC 1<br>Active | MCCC 2<br>Standby | CPCC 1<br>Standby | CPCC 2<br>Active | Backend                   |

| Log Server       | Boot<br>Server    |                   |                  |                           |

| Rack 001         | Rack 002          | Rack 003          | Rack 004         | Rack 005                  |

| Rack 006         | Rack 007          | Rack 008          | Rack 009         | Rack 010                  |

| Rack 100         | Rack 101          | Rack 102          | Rack 103         | Rack 104                  |

| Rack 105         | Rack 106          | Rack 107          | Rack 008         | Rack 109                  |

| Rack 110         | Rack 111          | Rack 112          | Rack 113         | Rack 114                  |

| Rack 115         |                   |                   |                  |                           |

|                  |                   |                   | Power<br>Systems | Heating<br>and<br>Cooling |

|        | TGM 0                 | TGM 1                 |

|--------|-----------------------|-----------------------|

| Board  | 101-1-7               | 110-1-7               |

| Status | Running               | Running               |

| Time 0 | 2007-123-09:45:34.010 | 2007-123-09:45:34.010 |

| Time 1 |                       |                       |

| Time 2 |                       |                       |

|        | Details               | Details               |

| Observation                  | Start Time            | Status      |   |

|------------------------------|-----------------------|-------------|---|

| V013Q22                      | 2007-123-09:30:00.000 | In progress |   |

| V013Q23                      | 2007-123:10:35:30.000 | Accepted    |   |

| V021A90                      | 2007-123-09:45:34.000 | In progress |   |

| V014Q01                      | 2007-124:11:05:00.000 | Rejected    |   |

| V01V22                       | 2007-122:23:30:00.000 | In progress |   |

| V01V23                       | 2007-123:10:15:00.000 | Accepted    |   |

| Test21 2007-123:09:30:00.000 |                       | In progress | ▼ |

|                              |                       | ►           |   |

| Antenna | Quad | #Boards | Board1  | Board2  |   |

|---------|------|---------|---------|---------|---|

| EVLA01  | 01   | 4       | 001-0-0 | 001-0-1 |   |

| EVLA02  | 02   | 4       | 001-0-4 | 001-0-5 |   |

| EVLA03  | 03   | 4       | 001-1-0 | 001-1-1 |   |

| EVLA04  | 04   | 4       | 001-1-4 | 001-1-5 |   |

| EVLA05  | 05   | 2       | 002-0-0 | 002-0-1 |   |

| EVLA06  | 05   | 2       | 002-0-2 | 002-0-3 |   |

| EVLA07  | 06   | 2       | 002-0-4 | 002-0-5 | ▼ |

|         |      |         |         | ►       |   |

#### NRC · CNRC

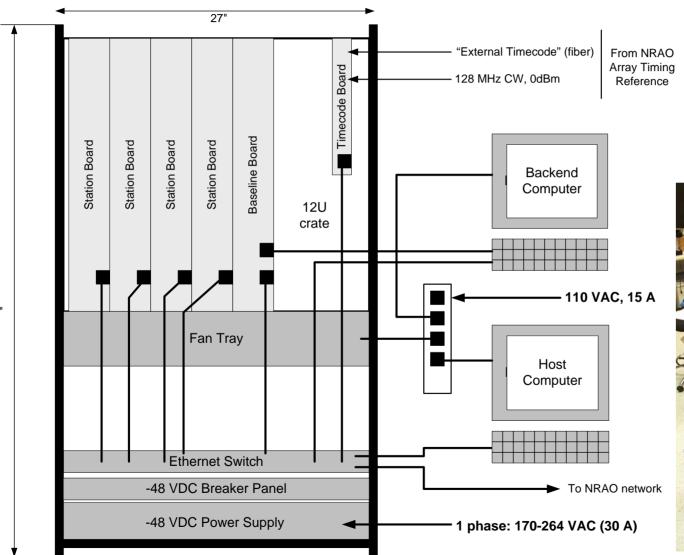

#### Individual Rack

WIDAR Correlator - Rack

#### Main

| Rack C        | 001 ——<br>te 0 —— |               |                   |                    |   |   |   |

|---------------|-------------------|---------------|-------------------|--------------------|---|---|---|

| Station Board | 1<br>•<br>•       | Station Board | Station Board 🛛 🐱 | Baseline Board 👴 🗗 | 5 | 6 |   |

| Cra           | te 1—             | 2             | 3                 | 4                  | 5 | 6 | 7 |

| Board | Status       | IP          | Туре |

|-------|--------------|-------------|------|

| 0     | ОК           | 123.23.1.1  | STB  |

| 1     | ОК           | 123.23.1.9  | STB  |

| 2     | ОК           | 123.23.1.17 | STB  |

| 3     | Initializing | 123.23.1.25 | STB  |

| 4     | OK           | 123.23.1.34 | BLB  |

| 5     |              |             |      |

| 6     |              |             |      |

| 7     | OK           | 123.23.1.60 | TGM  |

| 8     |              |             |      |

| 9     |              |             |      |

| 10    |              |             |      |

| 11    |              |             |      |

| 12    |              |             |      |

| 13    |              |             |      |

| 14    |              |             |      |

| 15    |              |             |      |

#### **Operator Log**

2007-90-11:15 Replaced STB1 2007-89-13:45 Initial installation

####

▼ ►

####

#### Station Board Top Level

#### Filter Control GUI

| creen Configu      | ration Hardware        |                         |                                |              |                                                              |           |

|--------------------|------------------------|-------------------------|--------------------------------|--------------|--------------------------------------------------------------|-----------|

| General            |                        |                         |                                |              | InOut                                                        |           |

| Design/Revision/V  | ersion: 01 1           | 7 State: running        |                                |              | Input: A V Output Enable:                                    | А 🖲 В     |

| Configuration File | /evla/widar/stb/fil    | ter/cfg_01.xml Browse   | 1                              |              | Input Delay: 37 Daisy Delay:                                 | 112       |

| FPGA Bit File      | /evla/widar/stb/fil    | ter/bit/abc Browse      | 1                              |              | Time Interval : 1234567                                      |           |

|                    | ,                      |                         |                                |              | Delay                                                        |           |

| VCI                |                        |                         | -Status-                       |              | Data Input Rate: 0  Demux Factor:                            | 1         |

| Input band width ( | MHz): 204              | 48 V Setup              | Input delay ca                 | libration:   | Delay Model:   External Phase Factor:                        | 0x400     |

| Input # bits:      |                        | 3 V                     | Input delay ad<br>System clock | ljust:       | Delay: 123456 Delay Rate:                                    |           |

| Input # bands:     |                        | 1 V Fbit:               | Delay Module<br>Read/Write:    | Input:       |                                                              |           |

| Input band:        |                        | 1 ▼ Flip: O             | Reset statu                    | sindicators  | Stage 1                                                      |           |

| Output band width  | n (MHZ): 128.000       |                         |                                |              | Product File: /evla/widar/stb/filter/s1prd/abc               | Browse    |

| Output band center | er (MHz): 192.000      |                         | CRC                            |              | Data Output Rate: 0 V                                        | XBAR      |

| Output # bits:     |                        | 4 🔻                     |                                | Auto         | Invalid Stretch Length : 32 Filter Delay :                   | 16        |

| Accumulation (inte | errupts): 100          |                         | View E                         | rror Counts  | Scale Factor : 1 Number of Taps :                            | 51        |

| Results file: /e   | vla/widar/stb/filter/f | fm/out/abc Browse       | Reset I                        | Error Counts |                                                              |           |

| Format             |                        |                         |                                |              |                                                              |           |

|                    |                        |                         |                                |              | Mixer Trig File /evla/widar/stb/filter/s2mix/abc             | Brow      |

| Output File:       |                        | /filter/fm/out/abc      |                                | Browse       | Use mixer Mixer Phase Model: C External                      |           |

| Select Data:       | 4 💌                    | Power on                | 12345 off                      | 12344        | Phase: 0x0000000                                             |           |

|                    |                        | Valids on               | 313 off                        | 312          | Phase Rate 0xFEDCBA9                                         |           |

| Select Clip:       | 1 🔻                    | Clip Count 12           | 234567                         |              | ,                                                            |           |

| RFI Detect Level:  | 0x17534                | RFI Detections          | 2                              |              | Stage 2                                                      |           |

| RFI Detect Length  | 256                    |                         |                                |              | Coefficient file /evla/widar/stb/filter/s2cof/abc            | Browse    |

| Sideband Flipper   | O On                   |                         |                                |              | Output Rate: Calculation Rate:                               | 0 •       |

| Quantizer Scaling: | 0x1234                 | Quantizer Power 12      | 234567                         |              | Invalid Stretch Length : 32 Filter Delay :                   | 16        |

| Quantizer # Bits:  | 4                      | Quantizer Clip Count    | 1                              |              | Scale Factor : 1 Number of Taps                              | 512 🔻     |

| Quantized State:   | C Auto -3              | Quantizer State Count   | 4                              | Histogram    | Stage 3                                                      |           |

| TEX Trig File      | /evla/widar/stb/       | /filter/fm/tex/trig/abc |                                | Browse       | Coefficient file /evla/widar/stb/filter/s3cof/abc            | Browse    |

| TEX Phase Model    | C External             |                         |                                |              | Output Rate: 8 Calculation Rate:                             | 0 •       |

| TEX Phase:         | 0x12345678             | TEX Valids              | 625                            |              | Invalid Stretch Length : 32 Filter Delay :                   | 16        |

| TEX Phase Rate:    | 0xFEDCBA9              | TEX Sums cos            | 1234 sin                       | 252          | Scale Factor : 1 Number of Taps                              | 512 🔻     |

| Deed/M/rite D      |                        | Pofroch                 |                                |              | Chara 1                                                      |           |

| -Read/Write R      | egisters               | Refresh                 |                                |              | Stage 4<br>Coefficient file /evla/widar/stb/filter/s4cof/abc | Browse    |

| Read Wr            | te Write/Read          | Sec:                    | Once                           |              |                                                              | 0 v       |

| Register: Write    | - Read:                | Test Port               |                                |              |                                                              |           |

|                    |                        | TP0 TP1                 | TP2 TP3<br>255 33              |              |                                                              | 16<br>512 |

|                    |                        | 5 17                    | 1 200 33                       |              | Scale Factor : Number of Taps                                | 512 🔻     |

#### NRC · CNRC

#### Correlator Software People

- Sonja Vrcic (Penticton)

- Coordinates overall design and specification.

- Virtual Correlator Interface (VCI) definition.

- Master Correlator Control Computer (MCCC) S/W.

- Bruce Rowen (Socorro)

- Correlator hardware control S/W (CMIB).

- Kevin Ryan (Socorro)

- GUI development and hardware control S/W.

- Martin Pokorny (Socorro)

- Correlator Backend software.

- Michael Rupen, John Romney, Bryan Butler, Ken Sowinski, Barry Clark, Bill Sahr (Socorro)

- Advisory capacity.

#### Correlator-related Software Issues

- Correlator output: ALMA Science Data Model (ASDM) must be qualified for EVLA use.

- On the surface ASDM looks all right in the sense that additions can be made to meet EVLA requirements.

- Is ALMA effort required and is it available?

- This issue is to be addressed later in the series of presentations.

- Preliminary plans to add "blocks" in the Correlator Back End (CBE).

- Additional Ethernet Switch and output Fast Data Formatter computer(s).

- Formatting to ASDM spec's will probably take place in the Fast Data Formatter.

- Details to be worked out.

- Virtual Correlator Interface (VCI) Transport protocol is to be defined.

- Potential unknown throughput issues could arise.

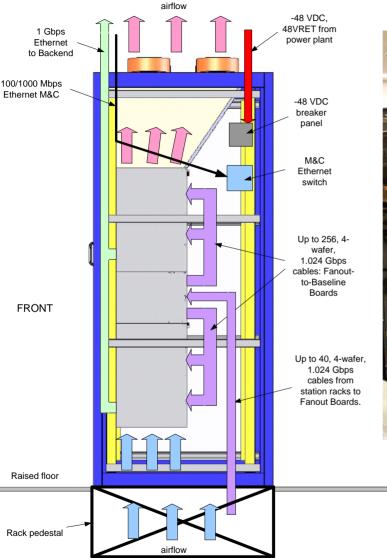

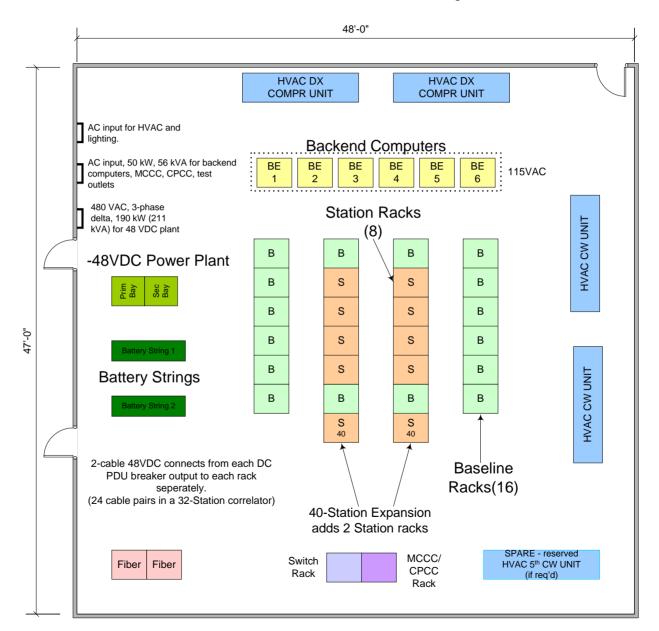

#### System Progress

- NRAO work on correlator room is progressing rapidly.

- Design of overall room layout is complete.

- **Environmental specifications have been developed.**

- Air flow & temperature: ~1700 cfm per rack, 15 °C.

- ElectroStatic Discharge (ESD)

- 90 nm devices used extensively (<1/1000 thickness of human hair)

- Humidity specs.

- Strict handling and servicing procedures.

- Air quality

- ISO 14644-1 class 8 + MERV 13 filter.

- Racks

- "Thermal prototypes" have been built and tested.

- **"Mechanical prototypes" ditto.**

- **Preliminary fabrication plan is being developed.**

- Preliminary installation plan is being developed.

- Power plant specifications/RFP draft written for acquisition this fiscal year (ends Mar 31/07).

#### Correlator Rack Layout

#### **NRC** · **CNRC** ElectroStatic Discharge (ESD)

**Correlator Testing**

- Production correlator chip tests

- Functional acceptance test by supplier using DRAOsupplied equipment.

- At speed, but not over temperature range.

- DRAO lab tests: special jig to be fabricated.

- HALT/HASS tests being investigated (advanced version of "burn-in").

- Unit PCB hardware tests during production:

- Fast functional tests performed at factory in DRAOsupplied equipment.

- Unit hardware tests after acceptance

- HALT/HASS tests of circuit boards (or equivalent).

- Extended functional tests.

#### Correlator Testing (cont'd)

- System Tests

- Prototype Stage

- Extended testing/debug cycle in lab all functions.

- Many self-tests, simulated observations.

- Should confer a high degree of reliability for On-the-Sky tests.

- On-the-sky Tests

- Final demonstration of prototype tests designed to be quasiindependent of EVLA S/W.

- Begin System Integration with EVLA software (continuing process).

- Hardware left at VLA site.

- Software Tests after On-the-Sky correlator delivered.

- Continued testing with hardware that will remain at the VLA.

- Understand interference (RFI) and the "clues" that the WIDAR system provides.

#### Test Configuration – Software View

#### On-the-Sky Test Setup

4' 5"

#### Installation Procedure

(Note: Dates from Apr/06 Long Term Schedule)

- 06-07: Install –48V DC power system.

- 06-07: Install underfloor cables.

- 08: Manufacture racks in Penticton.

- 08: Install overhead power distribution.

- 08: Install control computers, Ethernet switches, backend computers and other COTS equipment.

- 08-09: Install boards into racks in an order that maximizes scientific benefit.

####

#### **Preliminary** Installation Estimates

(Note: Dates from Apr/06 Long Term Schedule)

- Q4-06/Q1-07 power supply (-48 V DC) .

- Procurement, installation, training.

- 40 person-days of NRAO effort.

- Q3/Q4-07 signal cabling.

- Installation of inter-rack high-speed cabling.

- 512 pre-fab cables, 3 different lengths; 24 pre-fab power monitor & control cables.

- 52 person-days of NRAO effort.

- Q4-07/Q1-08 Racks

- 24 racks, pre-fabricated, tested in Penticton.

- 24 person days of NRAO effort.

- Q1-08 power cabling.

- Two cable runs: To distribution panel; distribution panel-to-racks.

- 20 person-days of NRAO effort.

#### NRC · CNRC

#### **Preliminary** Installation Estimates (cont'd)

- Q2-08 control computers, M&C Ethernet

- MCCC, CPCC, Ethernet switches, etc.

- 120 VAC power required.

- 8 person-days of NRAO effort.

- Q3-08 Back-end computers and equipment.

- Gbit Ethernet system.

- 20 person-days of NRAO effort.

- Q3-08/Q3-09 Board installation and test.

- Occasional NRAO effort.

- Total Est. NRAO installation effort:

- $\geq 8.2$  Person-Months.

# **EVLA Correlator Group**

#### DRAO-based.

#### NRAO-based.

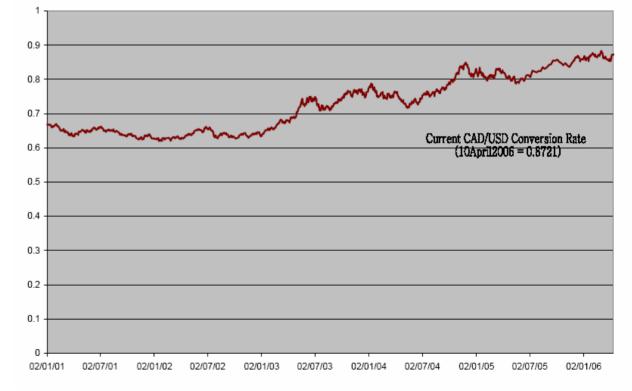

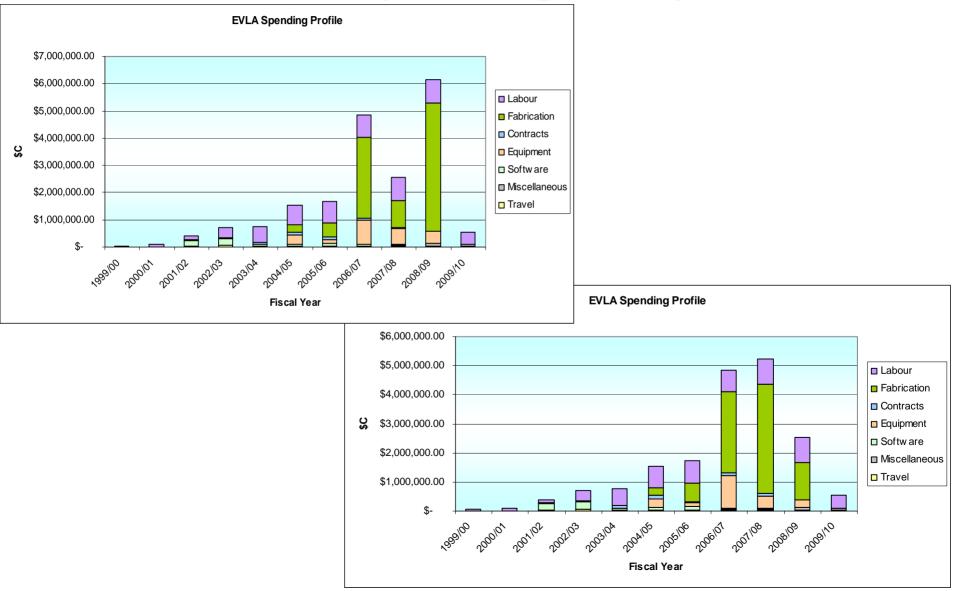

#### Funding in Canada – No Change

# Aug/03 – Canadian Treasury Board approval of submitted budget (\$C 20M over 5 years).

- Most spending in \$US.

- But see risk factors.

#### **Correlator Projected Spending Profile**

#### **NRC · CNRC** Correlator Summary Schedule

Very Uncertain Time Scale 2006 2007 2008 2009 2010 Q4 '05 Q1 '06 Q2 '06 Q3 '06 Q4 '06 Q1 '07 Q2 '07 Q3 '07 Q4 '07 Q1 '08 Q2 '08 Q3 '08 Q4 '08 Q1 '09 Q2 '09 Q3 '09 Q4 '09 Q1 '10 ID Task Name Stage 1 Prototype Hardware in Penticton Stage 1 Prototype PCB Acceptance Testing 3 Stage 2 Prototype Fabrication & Assembly Power Plant Delivered to VLA Site 20/03 Hardware/Software Integration Testing 6 Critical Design Review 05/07 Hardware for OTS Testing Sent to VLA 8 On-The-Sky Testing High-Speed Inter-Rack Cables Delivered to and Installed at VLA Site 10 Racks Delivered to and Installed at VLA Site 11 Stage 3 Production Hardware 12 System Integration & Testing @ Penticton Limited Production Hardware Sent to VLA 14 Stage 4 Production Hardware 15 Final Full Production Test & Burn-in in Penticton 16 Full Board Installation & Testing @ VLA 17 Commissioning - Turn off old correlator Prototype Software MCCC Software 20 CPCC Software 21 Correlator Backend Software (V1.0 Test, V2.0) 22 CMIB Production Software \*\* This schedule assumes no re-spins will be necessary. \*\* This schedule is the current quasi-optimistic view of the project. \*\* Long Term Schedule Modifications (from the previous edition - 09Mar2006): ----- Task 1: Stage 1 Prototype Hardware in Penticton end date has been pushed out by four weeks to 23June2006 due to delay in release of Station Board Work Order. ----- Task 2: Stage 1 Prototype PCB Acceptance Testing now pushed out by two weeks due to delay in release of Baseline Board Work Order. ----- Task 4: Power Plant Delivered to VLA Site has been added to schedule. ----- Task 9: High-Speed Inter-Rack Cables Delivered to and Installed at VLA Site has been added to schedule. ---- Task 10: Racks Delivered to and Installed at VLA Site has been added to schedule.

Project: EVLA\_LongTerm\_12Apr2006\_v1 Date: Wed 12/04/06

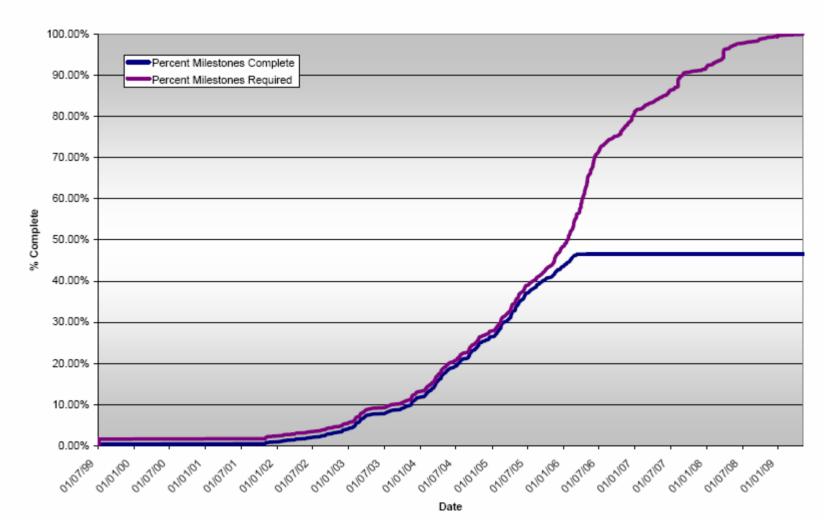

#### Milestone Progress

Percent Milestones Complete (10Mar2006)

- Schedule

- Detailed schedule periodically updated.

- Near-term (target) schedule updated weekly.

- Long-term schedule discussed monthly, and cross-checked against detailed schedule.

- Budget

- Projections updated with schedule.

- Bills of Materials (BOM's)

- 1000's of components.

- Maintenance required.

#### **Correlator Documentation**

- Master Document Tracking Spreadsheet Maintained at DRAO.

- 115 documents written so far, including "Memos".

- Additional 23 documents with designations and titles are anticipated.

#### Principal Design Reviews

- Three Design Reviews:

- Conceptual (CoDR Nov, 2001)

- Review architecture and overall design.

- Preliminary (PDR July, 2005)

- Review detailed designs before prototypes.

- Critical (CDR)

- Review system before "limited production" stage.

- Scheduled for Q2/Q3, 2007.

### Non-Technical Program Risks

- Funding

- Original allotment of funds was over five years.

- NRC management was made aware in Aug/03 that this does not fit the project spending profile they

decided that internal cash management could deal with the problem.

- Will have to apply for an extension, which in the present climate presents a risk.

- Worst case is that project could hypothetically be halted in April 2008.

- Active cash management at HIA, NRC level.

- Schedule slippage?

- Due to a slow start (already happened at the beginning).

- Concerns over procurement processes.

- This risk is retired. Major procurement contracts are in place except for power supply.

- Technical progress slower than the deliberately aggressive initial schedule.

- "Re-spins" will present additional schedule risk.

- Inadequate contingency?

- The contingency fractions are much smaller than most high-tech projects.

- Cost risk will be reduced quickly once prototypes are tested.

- Exchange-rate changes have been favourable to date.

- Inflation not being recognized in funding profile?

- Inflation is a corrosive influence.

# Technical Program Risks

- Technical risk is currently at a maximum

- Much design effort and prototype expenditure has taken place.

- Prototype hardware is being fabricated (or about to be fab'd), but not received/tested.

- But ...

- Considerable design effort expended to reduce technical risk.

- Finely divided testing schemes for circuit boards every path can be checked independently.

- Correlator chip underwent an independent test and verification process, including a major simulation campaign after the "place-and-route" stage.

- A separate Design for Manufacturability (DFM) analysis done for circuit boards results in a major reduction in risk.

- Formal system reliability analysis has been done, and will be updated.

- Funds and design effort has been expended to minimize technical risk.

- We are optimistic and confident that technical risk is reasonably low.

# Descoping

- The correlator is difficult to split, once designed, and saving is inefficient.

- Have not reconsidered descoping options since the budget is currently "under control".

- If the previously-mentioned non-technical risks become imminent concerns, then descoping options will have to be revisited.

- Are we meeting the required schedule?

- We are sticking with the original delivery date, although there is now some squeezing of activities towards the end.

- Are we over budget at this stage?

- Budget is slimly allocated, but we are not over budget.

- Are we planning to deliver on what we said we would do?

- Yes, with minor improvements.

- What are the major risks at this stage?

- Hypothetical funding difficulty in 2008.

- Technical risks should be reduced this year as prototypes are tested.

#### End