Architecture Manual, V 1.3.1, Apr 2001

## 32-Bit Single-Chip Microcontroller

Never stop thinking.

Edition 2000-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001-04-30 @ 15:16. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## 32-Bit Single-Chip Microcontroller

## Microcontrollers

Never stop thinking.

#### <Device>

### Revision History: 2000-01

Previous Version:

| Page | Subjects (major changes since last revision) |  |

|------|----------------------------------------------|--|

|      |                                              |  |

|      |                                              |  |

|      |                                              |  |

|      |                                              |  |

|      |                                              |  |

|      |                                              |  |

|      |                                              |  |

### Controller Area Network (CAN): License of Robert Bosch GmbH

### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

### mcdocu.comments@infineon.com

$\ge$

V 1.3.1

## TriCore Architecture v1.3 Manual

### About this document

This document was created with Adobe<sup>®</sup> FrameMaker<sup>®</sup> 5.5.6 at Infineon Technologies, 1730 North First Street, San Jose, California 95112, USA. This document is not controlled. No distribution list is maintained and the reader is responsible for ensuring that he/she is not using an obsolete version.

Your comments are invited via e-mail to: editor@infineon.com

### **Revision History**

| Release Version | Release Date | Notes                                                                                                                    |

|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------|

| 1.3.0           | Jan 13, 2000 | First release, v1.3 architecture                                                                                         |

| 1.3.1           | Jun 7, 2000  | Section numbering corrected, significant content changes to PSW and Instruction Set chapter, reformatted document        |

| 1.3.2           | Aug 14, 2000 | Significant improvements to Chapter 6, 7, 9 and some minor changes in LCXO description and some instruction descriptions |

© Infineon Technologies Corp., 2000. All Rights Reserved.

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of noninfringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Architecture Manual

2001-04-30 @ 15:16

| Table  | of | Contents |

|--------|----|----------|

| i ubic | ~  | Contento |

### Page

## TriCore Architecture v1.3 Manual i Architecture Overview 1

| 1    | Architecture Overview    | 2 |

|------|--------------------------|---|

| 1.1  | Feature Overview         | 3 |

| 1.2  | Program State Registers  | 3 |

| 1.3  | Data Types               |   |

| 1.4  | Addressing Modes         | 5 |

| 1.5  | Instruction Formats      | 5 |

| 1.6  | Tasks and Contexts       | 5 |

| 1.7  | Interrupt System         | 7 |

| 1.8  | Trap System              |   |

| 1.9  | Protection System        | 7 |

| 1.10 | Memory Management System | 8 |

| 1.11 | Reset System             | 9 |

| 1.12 | Debug System             | 9 |

| Prog | ramming Model 11         |   |

| 2    | Programming Model1       | 2 |

| 2.1  | Data Types               | 2 |

|      |                          |   |

|     |                  | ~ |

|-----|------------------|---|

| 2.4 | Addressing Model | 6 |

| 2.3 | Memory Model 1   | 5 |

|     | Data Formats 1   |   |

|     | Butta Typee      |   |

## Core Registers 23

| 3    | Core Registers               | 24 |

|------|------------------------------|----|

| 3.1  | Access to the Core Registers | 25 |

| 3.2  | General-Purpose Registers    | 25 |

| 3.3  | Program State Information    | 27 |

| 3.4  | Context Management Registers | 30 |

| 3.5  | Stack Management             | 33 |

| 3.6  | Interrupt and Trap Control   | 34 |

| 3.7  | System Control Registers     | 37 |

| 3.8  | MMU Registers                | 37 |

| 3.9  | Memory Protection Registers  | 38 |

| 3.10 | Debug Registers              | 43 |

## Managing Tasks & Functions 45

| 4   | Managing Tasks & Functions46             |

|-----|------------------------------------------|

| 4.1 | Upper and Lower Contexts 46              |

| 4.2 | Task Switching Operation                 |

| 4.3 | CSAs and Context Lists                   |

| 4.4 | Context Switching with Interrupts 50     |

| 4.5 | Context Switching with Function Calls 51 |

| 4.6 | Context Save/Restore Examples            |

### Table of Contents

## Interrupt System 57

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>Traps                              | Interrupt System       9         Service Request Node       9         Interrupt Control Unit       9         Entering an Interrupt Service Routine       9         The Interrupt Vector Table       9         Usage of the TriCore Interrupt System       9         CPU Service Request Nodes       9         73       73                                                             | 59<br>52<br>55<br>56<br>57                         |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 6<br>6.1<br>6.2<br>6.3<br>Memo                                                    | Traps       Trap Types         Trap Handling       Trap Descriptions         Trap Management 85                                                                                                                                                                                                                                                                                       | 74<br>77                                           |

| 7<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br><b>Protec</b> | Memory Management       a         Address Spaces       a         Address translation       a         Translation Lookaside Buffers       a         Cacheability       a         Protection       a         Multiple Address Spaces       a         MMU traps       a         MMU instructions       a         MMU Special Function Registers       a         Stion System 103       a | 37<br>38<br>39<br>90<br>91<br>92<br>92<br>92       |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>Instruc                                          | Protection System       10         Direct and Page Table Entry Addressing       10         Protection System Registers       10         Sample Protection Register Set       11         Memory Access Checking       17         Ction Set Overview 115       15                                                                                                                       | 04<br>04<br>11                                     |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9           | Instruction Set Overview11Arithmetic Instructions12Compare Instructions12Bit Operations13Address Arithmetic13Address Comparison13Branch Instructions13Load and Store Instructions13Context Related Instructions13System Instructions13                                                                                                                                                | 16<br>26<br>30<br>32<br>32<br>32<br>33<br>36<br>38 |

|         | 16-bit Instructions                    |

|---------|----------------------------------------|

| 10      | TriCore Instruction Set                |

| 10.1    | Instruction Syntax                     |

| 10.2    | Instruction Operation                  |

|         | Status                                 |

| 10.4    | Instruction Descriptions               |

| Global  | PartnerChip for Systems on Silicon 301 |

| Total ( | Quality Management 305                 |

| Index   | 307                                    |

# Architecture Overview

### 1 Architecture Overview

TriCore is the first single-core 32-bit microcontroller-DSP architecture optimized for real-time embedded systems. TriCore unifies the best of 3 worlds - real-time capabilities of microcontrollers, computational prowess of DSPs, and highest performance/price implementations of RISC load-store architectures.

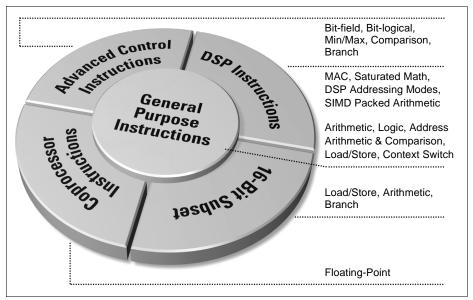

Figure 1-1 shows a high-level view of the architecture.

### Figure 1-1 TriCore: A Modular Instruction Set Architecture

The Instruction Set Architecture (ISA) supports a uniform, 32-bit address space, with optional virtual addressing and memory-mapped I/O. It allows for a wide range of implementations, ranging from simple scalar to superscalar. Furthermore, the ISA is capable of interacting with different system architectures, including those with multiprocessing. This flexibility at the implementation and system levels allows for different trade-offs between performance and cost at any point in time.

To support TriCore implementations with 32-bit instructions and simplified instruction fetching, the entire architecture is represented in 32-bit instruction formats. In addition, the architecture includes 16-bit instruction formats for the most frequently occurring instructions. These instructions significantly reduce code space, lowering memory requirements, system cost, and power consumption.

Real-time responsiveness is largely determined by interrupt latency and context-switch time. The high-performance architecture minimizes interrupt latency by avoiding long multicycle instructions

and by providing a flexible hardware-supported interrupt scheme. Furthermore, the architecture supports fast context switching.

### 1.1 Feature Overview

- 32-bit architecture

- 4-GByte virtual or physical data, program, and input/output address spaces

- Full-featured memory management system

- 16-/32-bit instructions for reduced code size

- Low interrupt latency

- Fast automatic context switching

- Multiply-accumulate unit

- Saturating integer arithmetic

- Bit handling

- Packed data operations

- Zero-overhead loop

- Byte and bit addressing

- Little-endian byte ordering

- Flexible interrupt prioritization scheme

- Memory protection

- Debug support

- Flexible power management

### 1.2 Program State Registers

The program state registers consist of 32 General-purpose Registers (GPRs), two 32-bit registers with program status information (PCXI and PSW), and a Program Counter (PC). PCXI, PSW, and PC are Core Special Function Registers (CSFRs).

## Architecture Overview Data Types

2001-04-30 @ 15:16

| 31 0                 | <u>31 0</u>         | 31     | ( |

|----------------------|---------------------|--------|---|

| A15 (Implicit Addr.) | D15 (Implicit Data) | PCXI   |   |

| A14                  | D14                 | PSW    |   |

| A13                  | D13                 | PC     |   |

| A12                  | D12                 |        |   |

| A11 (Return Addr.)   | D11                 |        |   |

| A10 (Stack Pointer)  | D10                 |        |   |

| A9                   | D9                  |        |   |

| A8                   | D8                  |        |   |

| A7                   | D7                  |        |   |

| A6                   | D6                  |        |   |

| A5                   | D5                  |        |   |

| A4                   | D4                  |        |   |

| A3                   | D3                  |        |   |

| A2                   | D2                  |        |   |

| A1                   | D1                  |        |   |

| A0                   | D0                  |        |   |

| Address              | Data                | System |   |

### Figure 1-2 Program State Registers

The 32 General-purpose Registers (GPRs) are divided into sixteen 32-bit data registers (D0 through D15); and sixteen 32-bit address registers (A0 through A15). Four GPRs have special functions: D15 is used as an implicit data register, A10 is the Stack Pointer (SP), A11 is the return address register, and A15 is the implicit address register.

Registers 0-7 are called the lower registers and 8-15 are called the upper registers.

Registers A0 and A1 in the lower address registers and A8 and A9 in the upper address registers are defined as system global registers. These registers are not included in either context partition, and are not saved and restored across calls or interrupts. The operating system normally uses them to reduce system overhead.

The PCXI and PSW registers contain status flags, previous execution information, and protection information.

### 1.3 Data Types

The TriCore instruction set supports operations on Booleans, bit strings, characters, signed fractions, addresses, signed and unsigned integers, and single-precision floating-point numbers. Most instructions work on a specific data type, while others are useful for manipulating several data types.

### 1.4 Addressing Modes

Addressing modes allow load and store instructions to efficiently access simple variables and data elements within data structures such as records, randomly and sequentially accessed arrays, stacks, and circular buffers. Simple variables and data elements are 1, 8, 16, 32, or 64 bits wide.

The addressing modes provide efficient compilation of C, easy access to peripheral registers, and efficient implementation of typical DSP data structures (circular buffers for filters and bit-reversed indexing for FFTs). The following 7 addressing modes are supported in the architecture.

- Absolute

- Base + Short Offset

- Base + Long Offset

- Pre-increment or decrement

- Post-increment or decrement

- Circular

- Bit Reverse

### 1.5 Instruction Formats

The architecture supports both 16- and 32-bit instruction formats. All instructions have a 32-bit format. The 16-bit instructions are a subset of the 32-bit instructions, chosen because of their frequency of use; they are included to reduce code space.

#### 1.6 Tasks and Contexts

Throughout this book, the term task refers to an independent thread of control. There are 2 types of tasks: Software-managed Tasks (SMTs) and Interrupt Service Routines (ISRs). Software-managed tasks are created through the services of a real-time kernel or OS, and dispatched under the control of scheduling software. ISRs are dispatched by hardware in response to an interrupt. In this architecture, ISR refers only to the code that is invoked by the hardware directly. Software-managed tasks are sometimes referred to as user tasks, assuming that they will execute in user mode.

Each task is allocated its own permission level. The individual permissions are enabled/disabled primarily by I/O mode bits in the Program Status Word (PSW).

Associated with any task is a set of state elements known collectively as the task's context. The context is everything the processor needs in order to define the state of the associated task and enable its continued execution. It includes the CPU general-purpose registers that the task uses, the task's Program Counter (PC), and its Program Status Information (PCXI and PSW). The TriCore architecture efficiently manages and maintains the tasks' contexts through hardware.

### 1.6.1 Upper and Lower Contexts

The context is subdivided into the upper context and the lower context (Figure 1-3). The upper context consists of the upper address registers, A10-A15, and the upper data registers, D8-D15. These registers are designated as non-volatile, for purposes of function calling. The upper context also includes the PCXI and PSW registers.

The lower context consists of the lower address registers, A2 through A7, the lower data registers, D0 through D7, and the PC.

Both upper and lower contexts include the PCXI link word. Contexts are saved in fixed-size areas (see next section); they are linked together *via* the link word.

The upper context is saved automatically on interrupts and is restored on returns. The lower context is saved and restored explicitly by the ISR if the ISR needs to use more registers than are provided by the upper context.

| Lower Context    | Upper Context    |

|------------------|------------------|

| D7               | D15              |

| D6               | D14              |

| D5               | D13              |

| D4               | D12              |

| A7               | A15              |

| A6               | A14              |

| A5               | A13              |

| A4               | A12              |

| D3               | D11              |

| D2               | D10              |

| D1               | D9               |

| D0               | D8               |

| A3               | A11 (RA)         |

| A2               | A10 (SP)         |

| Saved PC         | PSW              |

| PCXI (Link Word) | PCXI (Link Word) |

### Figure 1-3 Upper and Lower Contexts

### 1.6.2 Context Save Areas

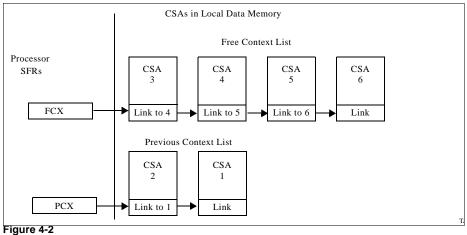

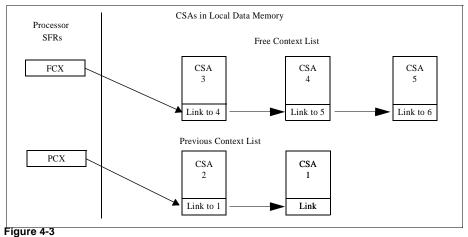

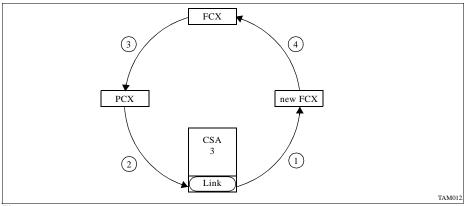

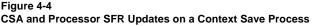

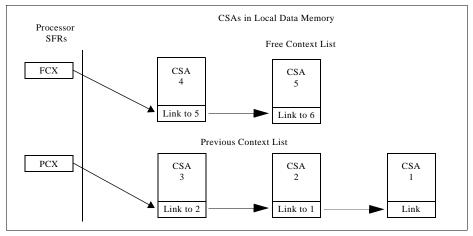

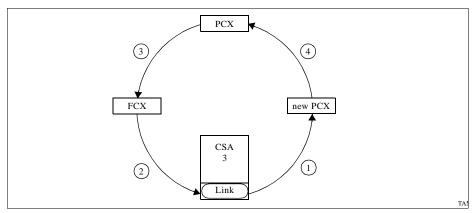

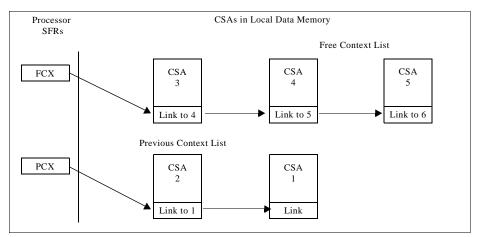

The architecture uses linked lists of fixed-size Context Save Areas (CSAs) which accommodate systems with multiple interacting threads of control. A CSA is 16 words of memory storage, aligned on a 16-word boundary. A single CSA can hold exactly 1 upper or 1 lower context. Unused CSAs are linked together on a free list. They are allocated from the free list as needed, and returned to it when no longer needed. The processor hardware handles the allocation and freeing. They are transparent to the applications code. Only the system start-up code and certain OS exception handling routines need to access the CSA lists and memory storage explicitly.

### 1.6.3 Fast Context Switching

To increase performance, the architecture implements a uniform context-switch mechanism for function calls, interrupts, and traps. In all cases, the task's upper context is automatically saved and restored by hardware; saving (and restoring) the lower context is left as an option for the new task.

Fast context switching is further enhanced by the TriCore's unique memory subsystem design, which allows a complete upper or lower context to be saved in as little as 2 clock cycles.

### 1.7 Interrupt System

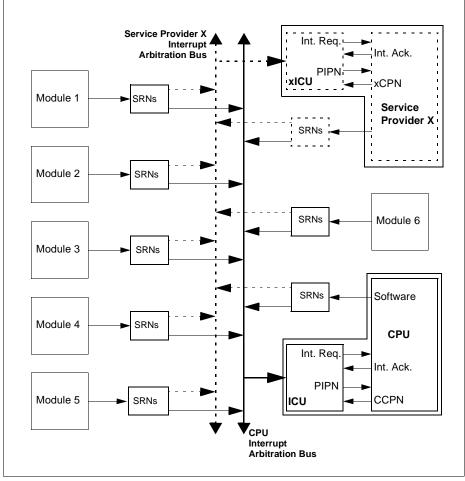

In this manual, a service request is defined as an interrupt request from a peripheral, a DMA request, or an external interrupt. For simplicity, a service request may also be referred to as an interrupt.

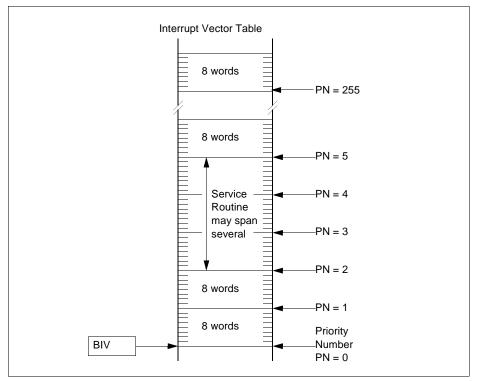

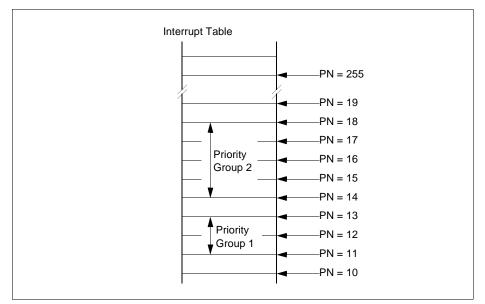

The entry code for the ISR is a block within a vector of code blocks. Each code block provides an entry for one interrupt source. Each source is assigned a priority number. All priority numbers are programmable. The service routine uses the priority number to determine the location of the entry code block.

The prioritization of service routines enables nested interrupts. A service request can interrupt the servicing of a lower priority interrupt. Interrupt sources with the same priority cannot interrupt each other.

### 1.8 Trap System

A trap occurs as a result of an exception within one of the following 8 classes:

- Internal protection

- Instruction errors

- Context management

- Memory management

- Internal bus and peripheral errors

- Assertion

- System call

- Non-maskable interrupt

The entry code for the trap handler is comprised of a vector of code blocks. Each code block provides an entry for one trap. When a trap is taken, the trap's Trap Identification Number (TIN) is placed in data register D15. The trap handler uses the TIN to identify precisely the cause of the trap.

### 1.9 Protection System

The protection system allows the programmer to assign access permissions to memory regions for both data and code. This capability is useful for protecting core system functionality from bugs that may have slipped through testing and from transient hardware errors.

The TriCore's protection system also provides the essential features needed to isolate errors, and thus facilitates debugging.

### 1.10 Memory Management System

The principal features of the TriCore memory management include:

- 4-GByte virtual address space divided into sixteen 256 MB segments

- 4-GByte physical address space divided into sixteen 256 MB segments

- Addressing by direct translation or via Page Table Entries (PTE)

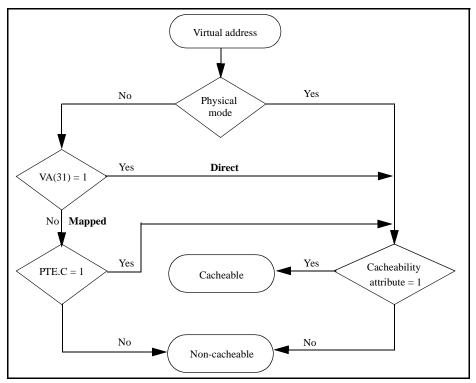

- Two addressing modes: physical and virtual (physical page attributes override virtual page attributes)

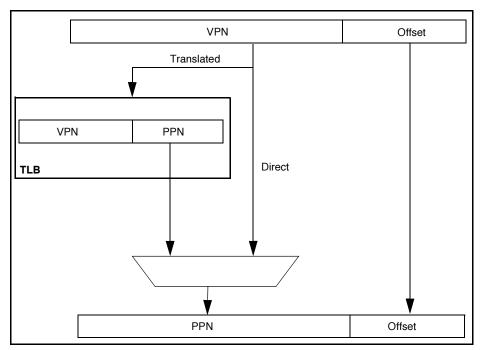

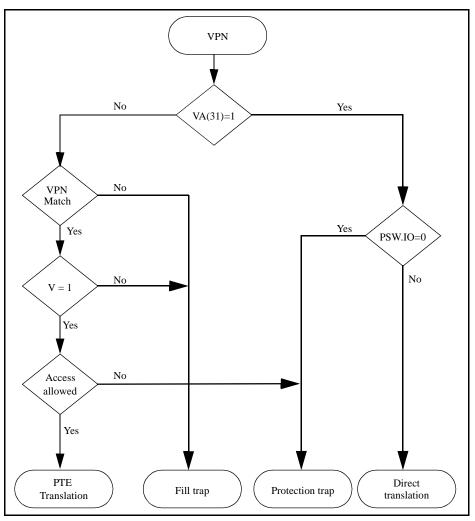

The virtual address space is divided into 16 segments of 256 MB each. The physical address space is also divided into 16 segments of 256 MB each. Virtual addresses are always translated into physical addresses before accessing memory.

The virtual address is translated into a physical address using either direct translation or Page Table Entry (PTE) translation.

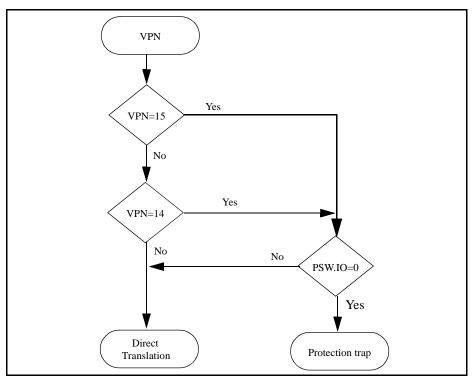

- Direct translation: If the virtual address belongs to the upper half of the virtual address space then

the virtual address is directly used as the physical address. If the virtual address belongs to the

lower half of the address space, then the virtual address is used directly as the physical address

if the processor is operating in Physical mode.

- PTE translation: If the virtual address belongs to the lower half of the address space, then the virtual address is translated using a Page Table Entry if the processor is operating in Virtual mode.

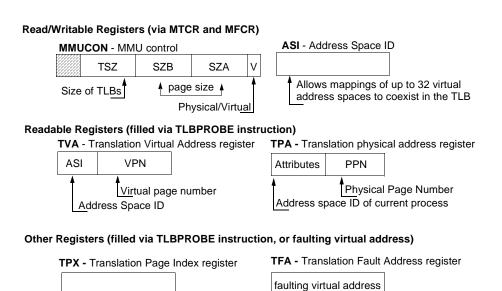

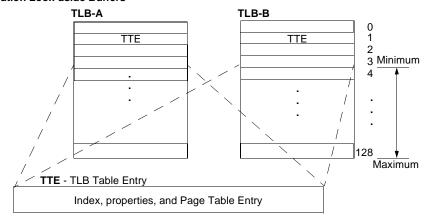

PTE translation is performed by replacing the Virtual Page Number (VPN) of the virtual address by a Physical Page Number (PPN) to obtain a physical address. Six memory-mapped MMU Core Special Function Registers (CSFRs) control the memory management system.

### 1.10.1 Permission Levels

TriCore's embedded architecture allows each task to be allocated the specific permission level it needs to perform its function. Individual permissions are enabled through the I/O mode bits in the PSW. The 3 permission levels are User-0, User-1, and Supervisor:

- User-0 mode

- Used for tasks that do not access peripheral devices.

- Tasks at this level do not have permission to enable or disable interrupts.

- User-1 mode

- Used for tasks that access common, unprotected peripherals.

- Accesses typically include read/write accesses to SIO ports and read accesses to timers and most I/O status registers.

- Tasks at this level may disable interrupts.

- Supervisor mode

- Permits read/write access to system registers and all peripheral devices.

- Tasks at this level may disable interrupts.

### 1.10.2 Protection Model

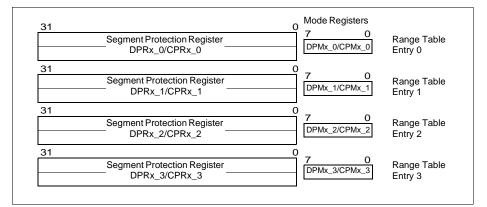

The memory protection model for the TriCore architecture is based on address ranges, where each address range has an associated permission setting. Address ranges and their associated

permissions are specified in 2-4 identical sets of tables residing in the Core Registration Function Register (CSFR) space. Each set is referred to as a Protection Register Set (PRS).

When the protection system is enabled, the TriCore checks every load/store and instruction fetch address for legality before performing the access. To be legal, the address must fall within 1 of the ranges specified in the currently selected PRS, and permission for that type of access must be present in the matching range.

### 1.11 Reset System

Most of the reset functions and options are located external to the core and are not described in this architecture manual. Several events can force a reset of the TriCore device:

- Power-On Reset

- Activated through an external pin when the power to the device is turned on (cold reset).

- Hard Reset

- Activated through an external pin during run time (warm reset).

- Soft Reset

- Activated through a software write to a reset request register which has a special protection mechanism to prevent accidental accesses.

- Implementation-specific controls in this register facilitate either partial or full reset of the device.

- Watchdog Timer Reset

- Activated through an error condition detected by a watchdog timer.

- Wake-up Reset

- Activated through an external pin to wake the device from a power saving mode.

A reset status register allows the core to check which of the triggers caused the reset.

### 1.12 Debug System

The TriCore contains mechanisms and resources to support on-chip debugging. These are used by the Debug Control Unit. Most functions and details of the Debug Control Unit are implementation-specific. This document does not provide further descriptions of the debug control unit and its associated registers. Please contact your local Infineon sales office for literature or further information.

## Architecture Overview Debug System

2001-04-30 @ 15:16

# **Programming Model**

### Programming Model Data Types

2001-04-30 @ 15:16

### 2 Programming Model

This chapter discusses the following aspects of the TriCore architecture that are visible to software:

- Supported data types

- Formats of data types in registers and memory

- Various addressing modes that the architecture provides

- The memory model

#### 2.1 Data Types

The TriCore instruction set supports operations on Booleans, bit strings, characters, signed fractions, addresses, signed and unsigned integers, and single-precision floating-point numbers. Most instructions operate on a specific data type, while others are useful for manipulating several data types.

### 2.1.1 Boolean

A Boolean is either TRUE or FALSE. TRUE is the value one (1) when generated and non-zero when tested; FALSE is the value zero (0). Booleans are produced as the result in comparison and logic instructions, and are used as source operands in logical and conditional jump instructions.

### 2.1.2 Bit String

A bit string is a packed field of bits. Bit strings are produced and used by logical, shift, and bit field instructions.

### 2.1.3 Character

A character is an 8-bit value that is a very short unsigned integer. No specific coding is assumed.

### 2.1.4 Signed Fraction

The TriCore architecture supports 16-/32-bit signed fractional data for DSP arithmetic. Data values in this format have a single high-order sign bit, where 0 represents positive (+) and 1 represents negative (–), followed by an implied binary point and fraction. Thus their values are in the range [-1,1).

### 2.1.5 Address

An address is a 32-bit unsigned value.

### 2.1.6 Signed/Unsigned Integers

Signed and unsigned integers are normally 32 bits. Shorter signed or unsigned integers are signextended or zero-extended to 32 bits when loaded from memory into a register. Multi-precision integers are supported with addition and subtract using carry. Integers are considered to be bit strings for shifting and masking operations. Multi-precision shifts can be done using a combination of single-precision shifts and bit field extracts.

### 2.1.7 IEEE-754 Single-precision Floating-point Number

Depending on the particular implementation of the core architecture, IEEE-754 floating-point numbers are supported by co-processor hardware instructions or by software calls to a library.

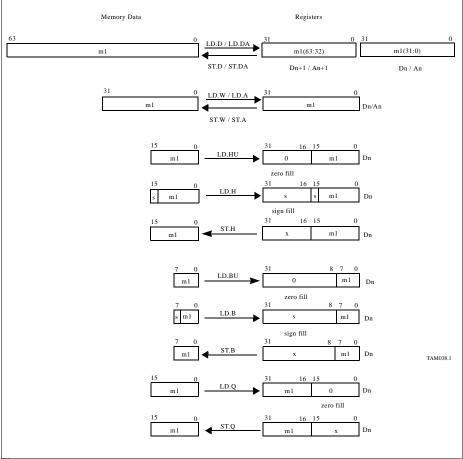

### 2.2 Data Formats

All the General-purpose registers (GPRs) are 32 bits wide, and most instructions operate on word (32-bit) values. When byte or halfword data elements are loaded from memory, they are automatically sign-extended or zero-extended to fill the register. The type of filling is implicit in the load instruction: e.g., LD.B to load a byte with sign extension, vs. LD.BU to load a byte with zero extension.

Alignment requirements differ for addresses and data. Address variables, loaded into or stored from address registers, must always be word-aligned. For transfers between data registers and memory, there is some relaxation of the natural alignment restrictions. In most cases, data may be aligned on any halfword boundary, regardless of size. This facilitates the use of packed arithmetic operations in DSP applications, by allowing two or four packed 16-bit data elements to be loaded or stored together on any halfword boundary. However, there are some restrictions of which programmers must be aware. Specifically:

- The LDMST and SWAP instructions require their operands to be word-aligned;

- Halfword alignment for LD. D and ST. D is only allowed when the source or destination address is targetted at local data or cached memory. For all other addresses doubleword accesses must be word-aligned.

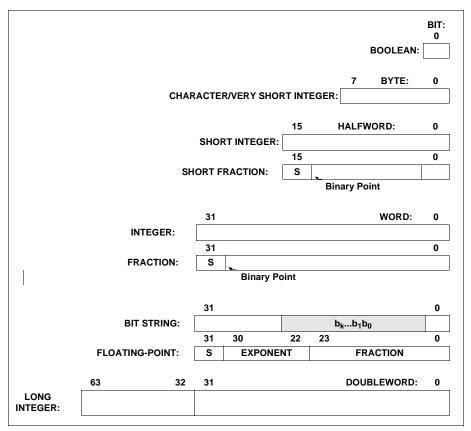

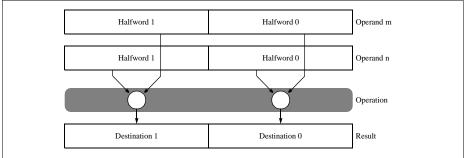

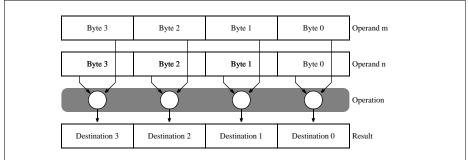

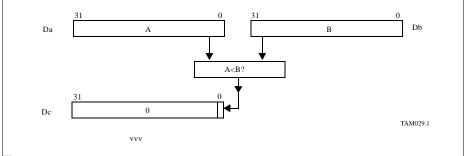

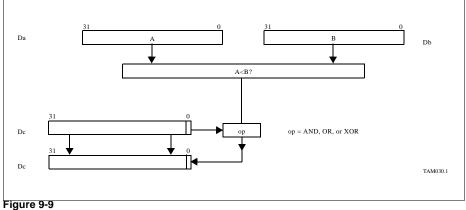

Figure 2-1 illustrates the data types supported.

### Programming Model Data Formats

Architecture Manual

2001-04-30 @ 15:16

### Figure 2-1 Supported Data Formats

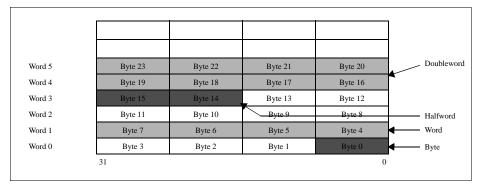

The data memory and CPU registers store data in little-endian byte order (the least-significant bytes are at lower addresses). Figure 2-2 illustrates the byte ordering. Little-endian memory referencing is used consistently for data and instructions.

Architecture Manual 2001-04-30 @ 15:16

Infineon

### Figure 2-2 Byte Ordering

### 2.3 Memory Model

The TriCore architecture has an address width of 32 bits and can access up to 4 GB of memory. The address space (Table 2-1) is divided into 16 regions or segments (0 through 15). Each segment is 256 MB. The upper 4 bits of an address select the specific segment. The first 16 KB of each segment can be accessed using either absolute addressing or absolute bit addressing.

### Table 2-1 Physical Address Space

| Address                         | Segments | Description                                                                                                 |

|---------------------------------|----------|-------------------------------------------------------------------------------------------------------------|

| 0xFFFF FFFF<br>:<br>0xE000 0000 | 14 - 15  | non-speculative access<br>no User 0 access                                                                  |

| 0xDFFF FFFF<br>:<br>0x8000 0000 | 8-13     | normal access<br>Detailed limitations are implementation-specific.<br>See device-specific System User Guide |

| 0x7FFF FFFF<br>:<br>0x0000 0000 | 0-7      | reserved                                                                                                    |

Many data accesses use addresses computed by adding a displacement to the value of a base address register. Using a displacement to cross one of the segment boundaries is not allowed, and, if attempted, will cause a trap. This restriction allows direct determination of the accessed segment from the base address.

Segments 0-7 are reserved for future use. Accesses to these segments will cause a trap. Accesses to segment 14 and 15 are guaranteed to be non-speculative but they are not accessible in User 0 mode. These segments can thus be used for mapping peripheral registers. The Core Special Function Registers (CSFRs) are mapped to a 64-KB space in the memory map. The base location of this 64-KB space is implementation-dependent. Segments 8-13 will have futher limitations placed

upon them in some implementations. For example, specific segments for program and data may be defined by device-specific implementations. Other details of the memory mapping are implementation-specific. Please refer to the device-specific User's Manual.

### 2.4 Addressing Model

### 2.4.1 Addressing Modes

Addressing modes (Table 2-2) allow load and store instructions to access simple data elements such as records, randomly and sequentially accessed arrays, stacks, and circular buffers effectively within data structures. Simple data elements are 8, 16, 32, or 64 bits wide.

The addressing modes were selected to support efficient compilation of C, easy access to peripheral registers, and efficient implementation of typical DSP data structures (circular buffers for filters and bit-reversed indexing for FFTs).

| Table 2-2            |       |

|----------------------|-------|

| Supported Addressing | Modes |

| Addressing Mode | Address Register Use  | Offset Size (bits) |

|-----------------|-----------------------|--------------------|

| absolute        | none                  | 18                 |

| base+offset     | address register      | 10 <sup>1)</sup>   |

| pre-increment   | address register      | 10                 |

| post-increment  | address register      | 10                 |

| circular        | address register pair | 10                 |

| bit-reverse     | address register pair | —                  |

1) A subset of memory operations support a base + long offset addressing mode which provides a 16-bit offset.

The instruction formats were chosen to provide as many bits of address as possible for absolute addressing and as large of range of offsets as possible for base+offset addressing.

Note it is possible for an address register to be both the target of a load and an update associated with a particular addressing mode. For example, in the following case, the contents of the address register are not architecturally defined:

ld.a a0, [a0+]4

In a similar manner, consider the following case:

st.a [+a0]4, a0

It is not architecturally defined whether the original or updated value of a0 is stored into memory. This is true for all addressing modes in which there is an update of the address register.

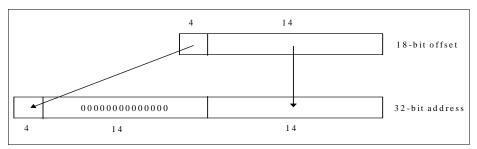

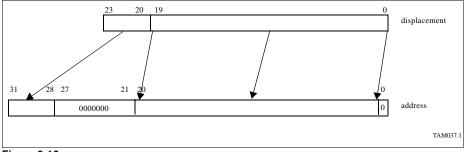

### 2.4.1.1 Absolute Addressing

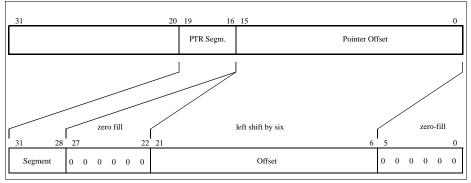

Absolute addressing is useful for referencing I/O peripheral registers and global data. It uses an 18bit constant specified by the instruction as the memory address. The full 32-bit address results from

| Infineon     |        |

|--------------|--------|

| Architecture | Manual |

moving the most significant 4 bits of the 18-bit constant to the most significant bits of the 32-bit address (Figure 2-3). The other bits are zero-filled.

### Figure 2-3 Translation of Absolute Address to Full Effective Address

### 2.4.1.2 Base+Offset Addressing

Base+offset is useful for referencing record elements, local variables (using SP as the base), and static data (using an address register pointing to the static data area).

The effective address is the sum of an address register and the sign-extended 10-bit offset.

A subset of the memory operations are provided with a base + long offset addressing mode. In this mode the offset is a 16-bit sign-extended value. This allows any location in memory to be addressed using a two instruction sequence.

### 2.4.1.3 Post-Increment Addressing

Post-increment and post-decrement addressing, where the latter is obtained by the use of a negative offset, may be used for forward or backward sequential access of arrays, respectively. Further, the two versions of the mode may be used to pop from a downward- or upward-growing stack, respectively.

The post-increment addressing mode uses the value of the address register as the effective address, and then updates this register by adding the sign-extended 10-bit offset to its previous value.

### 2.4.1.4 Pre-Increment Addressing

Pre-increment and pre-decrement addressing, where the latter is obtained by the use of a negative offset, may be used to push onto an upward- or downward-growing stack, respectively.

The pre-increment addressing mode uses the sum of the address register and the offset both as the effective address and as the value written back into the address register.

### 2.4.1.5 Circular Addressing

The primary use of circular addressing (Figure 2-4) is for accessing data values in circular buffers while performing filter calculations.

### Figure 2-4 Circular Addressing Mode

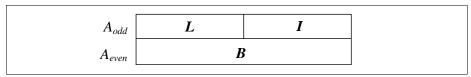

The circular addressing mode uses an address register pair to hold the state it requires. The even register is always a base address (B). The most significant half of the odd register is the buffer size (L). The least significant half holds the index into the buffer (I). The effective address is (B+I). The buffer occupies memory from addresses B to B+L-1.

The index is post-incremented using the following algorithm:

```

tmp = I + sign_ext(offset10);

if (tmp < 0)

I = tmp + L;

else if (tmp >= L)

I = tmp - L;

else

I = tmp;

```

The 10-bit offset is specified in the instruction word and is a byte-offset that can be either positive or negative. Note that correct "wrap around" behavior is guaranteed as long as the magnitude of the offset is smaller than size of the buffer.

To illustrate the use of circular addressing, consider a circular buffer consisting of 25 16-bit values. If the current index is 48, then the next item is obtained using an offset of 2 (2 bytes per value). The new value of the index "wraps around" to 0. Instead if we are at an index of 48 and use an offset of 4, the new value of the index is 2. If the current index is 4 and we use an offset of -8, then the new index is 46 (4-8+50).

In the end case, where a memory access runs off the end of the circular buffer (Figure 2-5), the data access also wraps round to the start of the buffer. For example, consider a circular buffer containing n+1 elements, where each element is a 16-bit value. If a load word is performed using the circular addressing mode and the effective address of the operation points to element n, the 32-bit result will contain element n in the bottom 16 bits and element 0 in the top 16 bits.

| Circular buffer of n 16-bit elements                                                            |      |  |            |          |    |   |    |   |

|-------------------------------------------------------------------------------------------------|------|--|------------|----------|----|---|----|---|

| 0                                                                                               | 1    |  |            |          | n- | 1 | n  |   |

| 15 0                                                                                            | 15 0 |  |            |          | 15 | 0 | 15 | 0 |

| Result of a circular addressing<br>load word with an effective<br>address pointing to element n |      |  | 0<br>31 16 | <i>n</i> | 0  |   |    |   |

### Figure 2-5 Circular Buffer End Case

The size and length of a circular buffer have the following restrictions:

- The start of the buffer must be aligned to a 64-bit boundary.

- An implementation is free to advise the user of optimal alignment of circular buffers etc., but must support the above.

- The length of the buffer must be a multiple of the data size, where the data size is determined from the instruction being used to access the buffer.

- For example, a buffer accessed using a load word instruction must be a multiple of 4 bytes in length, and a buffer accessed using a load double word instruction must be a multiple of 8 bytes in length.

If the above restrictions are not met, the implementation will take an alignment trap. An alignment trap is also taken if the index (I)  $\geq$  length (L).

### 2.4.1.6 Bit-reverse Addressing

Bit-reverse addressing is used to access arrays used in FFT algorithms. The most common implementation of the FFT ends with results stored in bit-reversed order (Figure 2-6).

### Programming Model Addressing Model

2001-04-30 @ 15:16

### Figure 2-6 Bit-Reverse Addressing

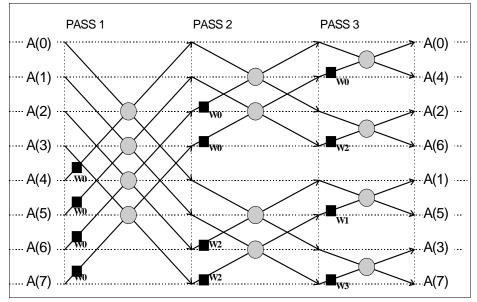

Bit-reverse addressing (Figure 2-7) uses an address register pair to hold the required state.

### Figure 2-7 Register Pair for Bit-Reverse Addressing

The even register is the base address of the array (B), the least-significant half of the odd register is the index into the array (I), and the most-significant half is the modifier (M) which is used to update I after every access.

The effective address is B+I. The index, I, is post-incremented and its new value is *reverse* [*reverse* (*I*) + *reverse* (*M*)]. The *reverse*(*I*) function exchanges bit *n* with bit (15-n) for n = 0, ..., 7.

To illustrate, for a 1024-point real FFT using 16-bit values, the buffer size is 2048 bytes. Stepping through this array using a bit-reverse index would give the sequence of byte indices: 0, 1024, 512, 1536, .... This sequence can be obtained by initializing I to 0 and M to 0x0400 (see Table 2-3).

### Table 2-3 1024-point FFT Using 16-bit Values

| l (decimal) | l (binary)                              | Reverse(I)      | Rev(I) + Rev(M)  |

|-------------|-----------------------------------------|-----------------|------------------|

| 0           | 000000000000000000000000000000000000000 | 000000000000000 | 000001000000000  |

| 1024        | 000001000000000                         | 000000000100000 | 000000100000000  |

| 512         | 000000100000000                         | 000000001000000 | 0000011000000000 |

| 1536        | 0000011000000000                        | 000000001100000 | 0000010001100000 |

The value of M required is given by buffer size/2 where the buffer size is given in bytes.

### 2.4.2 Synthesized Addressing Modes

This section describes how addressing not supported directly in the hardware addressing modes can be synthesized through short instruction sequences.

### 2.4.2.1 Indexed Addressing

Indexed addressing can be synthesized using the ADDSC.A instruction, which adds a scaled data register to an address register. The scale factor can be 1, 2, 4, or 8 for addressing indexed arrays of bytes, halfwords, words, or doublewords.

For support of addressing of indexed bit arrays, the ADDSC.AT instruction scales the index value by 1/8 (shifts right 3 bits) and adds it to the address register. The 2 low-order bits of the resulting byte address are cleared to give the address of the word containing the indexed bit. To extract the bit, the word containing it is loaded, and the bit index is used in an EXTR.U instruction. A bit field, beginning at the indexed bit position, can be extracted also. To store a bit or bit field at an indexed bit position, ADDSC.AT is used in conjunction with the LDMST (Load/Modify/Store) instruction.

### 2.4.2.2 PC-relative Addressing

PC-relative addressing is the normal mode for branches and calls. However, the TriCore architecture does not support direct PC-relative addressing of data. The main reason is that the separate on-chip instruction and data memories make data access to the program memory expensive. It typically adds 2 cycles of added access time.

When PC-relative addressing of data is required, the address of a nearby code label is placed into an address register and used as a base register in base + offset mode to access the data. Once the base register is loaded, it can be used to address other PC-relative data items nearby.

A code address can be loaded into an address register in various ways. If the code is statically linked—as it almost always is for embedded systems—then the absolute address of the code label is known, and can be loaded using the LEA instruction (Load Effective Address), or with a sequence to load an extended absolute address. The absolute address of the PC relative data is also known, and there is no need to synthesize PC-relative addressing.

### Programming Model Addressing Model

2001-04-30 @ 15:16

For code that is dynamically loaded, or assembled into a binary image from position-independent pieces without the benefit of a relocating linker, the appropriate way to load a code address for use in PC-relative data addressing is to use the JL (Jump and Link) instruction. A jump and link to the next instruction is executed, placing the address of that instruction into the return address register (A11). Before doing so, it is necessary to copy the actual return address of the current function to another register.

# **Core Registers**

### **Core Registers**

2001-04-30 @ 15:16

### 3 Core Registers

The TriCore architecture defines a set of Core Special Function Registers (CSFRs). These CSFRs control the operation of the core and provide status information about the core's operation. The CSFRs are split into the following groups:

- Program State Information

- Context Management

- Stack Management

- Interrupt and Trap Control

- System Control

- Memory Protection

- Memory Management

- Debug Control

The following sections describe these registers in detail. The CSFRs are complemented by a set of General-purpose Registers (GPRs). Table 3-1 shows all CSFRs and GPRs.

Most of the memory protection system and debug control unit is implementation-specific; therefore, this architecture manual only summarizes these topics. The reset functions and options are located in a block outside of the core; their functionality is briefly described in this manual. Please contact your local Infineon Sales office for more information on literature availability.

| Register Name/Acronym | Description                                           |

|-----------------------|-------------------------------------------------------|

| D0 – D15              | Data Registers                                        |

| A0 – A15              | Address Registers                                     |

| PSW                   | Program Status Word                                   |

| PCXI                  | Previous Context Information                          |

| PC                    | Program Counter (read only)                           |

| FCX                   | Free Context List Head Pointer                        |

| LCX                   | Free Context List Limit Pointer                       |

| ISP                   | Interrupt Stack Pointer                               |

| ICR                   | Interrupt Control Register                            |

| BIV                   | Base Address of Interrupt Vector Table                |

| BTV                   | Base Address of Trap Vector Table                     |

| SYSCON                | System Configuration Register                         |

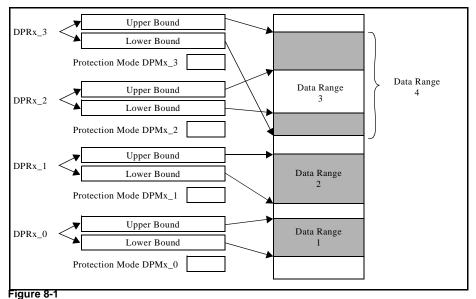

| DPRx_0 – DPRx_3       | Data Segment Protection Register Sets ( $x = 0 - 3$ ) |

| CPRx_0 – CPRx_3       | Code Segment Protection Register Sets ( $x = 0 - 3$ ) |

| DPMx_0 – DPMx_3       | Data Protection Mode Register Sets ( $x = 0 - 3$ )    |

| CPMx_0 – CPMx_3       | Code Protection Mode Register Sets $(x = 0 - 3)$      |

### Table 3-1 Core Register Map

#### Table 3-1 Core Register Map (cont'd)

| Register Name/Acronym | Description                          |

|-----------------------|--------------------------------------|

| DBGSR                 | Debug Status Register                |

| EXEVT                 | External Break Input Event Specifier |

| SWEVT                 | Software Break Event Specifier       |

| CREVT                 | Core SFR Access Event Specifier      |

| TRnEVT                | Trigger Event n Specifier (n = 0, 1) |

| MMUCON                | MMU Configuration register           |

| ASI                   | MMU Address Space Identifier         |

| TVA                   | MMU Translation Virtual Address      |

| ТРА                   | MMU Translation Physical Address     |

| ТРХ                   | MMU Translation Page Index           |

| TFA                   | MMU Translation Fault Address        |

#### 3.1 Access to the Core Registers

The core accesses the CSFRs through two instructions: MFCR and MTCR. The MFCR instruction (Move From Core Register) moves the contents of the addressed CSFR into a data register. MFCR can be executed on any privilege level. The MTCR instruction (Move To Core Register) moves the contents of a data register to the addressed CSFR. To prevent unauthorized writes to the CSFRs, the MTCR instruction can only be executed on the supervisor privilege level.

There are no instructions allowing bit, bit field or load-modify-store accesses to the CSFRs. The RSTV instruction (Reset Overflow Flags) resets only the overflow flags in the PSW, without modifying any of the other PSW bits. This instruction can be executed at any privilege level.

### 3.2 General-Purpose Registers

Figure 3-1 shows the GPRs. The 32-bit wide GPRs are split evenly into 16 data registers, or DGPRs, (D0 to D15) and 16 address registers, or AGPRs, (A0 to A15). Separation of data and address registers facilitates efficient implementations in which arithmetic and memory operations are performed in parallel. Several instructions allow the interchange of information between data and address registers in order to create or derive table indexes, etc. Two consecutive even-odd data registers can be concatenated to form 8 extended-size registers (E0, E2, E4, E6, E8, E10, E12, and E14), in order to support 64-bit values.

## Core Registers General-Purpose Registers

2001-04-30 @ 15:16

| Address GPRs (AGPRs)            | Data GPRs (DGPRs)            |                  |

|---------------------------------|------------------------------|------------------|

| 31 0                            | 31 0                         | 1                |

| A15 (implicit address register) | D15 (implicit data register) | >E14             |

| A14                             | D14                          | 5 14             |

| A13                             | D13                          | }_E12            |

| A12                             | D12                          | ∫ <sup>E12</sup> |

| A11 (Return Address / RA)       | D11                          |                  |

| A10 (Stack Pointer / SP)        | D10                          | }E10             |

| A9 (global address register)    | D9                           |                  |

| A8 (global address register)    | D8                           | E8               |

| A7                              | D7                           |                  |

| A6                              | D6                           | }E6              |

| A5                              | D5                           |                  |

| A4                              | D4                           | }E4              |

| А3                              | D3                           |                  |

| A2                              | D2                           | }E2              |

| A1 (global address register)    | D1                           |                  |

| A0 (global address register)    | D0                           | }E0              |

#### Figure 3-1 General-Purpose Registers

Registers A0, A1, A8, and A9 are defined as system global registers. Their contents are not saved and restored across calls, traps, or interrupts. Register A10 is used as the Stack Pointer (SP); register A11 is used to store the Return Address (RA) for calls and linked jumps and to store the return Program Counter (PC) value for interrupts and traps.

While the 32-bit instructions have unlimited use of the GPRs, many 16-bit instructions implicitly use A15 as their address register and D15 as their data register. This implicit use eases the encoding of these instructions into 16 bits.

In order to support 64-bit data values, an even/odd register pair holds these values. In the assembler syntax, these register pairs are either referred to as a pair of 32-bit registers (for example, D9/D8) or as an extended 64-bit register. For example, E8 is the concatenation of D9 and D8, where D8 is the least significant word of E8.

Core Registers Program State Information

2001-04-30 @ 15:16

Note that there are no separate floating-point registers—the data registers are used to perform floating-point operations. The floating-point data is saved/restored automatically using the fast context switch support.

The GPRs are an essential part of a task's context. When saving or restoring a task's context to and from memory, the context is split into the upper and lower contexts. Registers A2 through A7 and D0 through D7 are part of the lower context. Registers A10 through A15 and D8 through D15 are part of the upper context.

#### 3.3 Program State Information

The PC, PSW, and PCXI registers hold and reflect program state information. When storing and restoring a task's context, the contents of these registers are an important part of this procedure and are stored/restored or modified during this process.

#### 3.3.1 Program Counter

The 32-bit Program Counter (PC) is shown below. The PC contains the address of the instruction that is currently executing. The PC is part of a task's state information.

| 31              | 1 | 0 |

|-----------------|---|---|

| Program Counter |   | 0 |

#### 3.3.2 Program Status Word

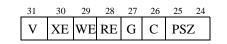

The **Program Status Word** (PSW) is a 32-bit register that contains task-specific architectural state not captured in the general purpose register values. The lower half holds control values and parameters related to the protection system. Included are the Protection Register Set (PRS), the I/ O privilege level (IO), the Interrupt Stack flag (IS), the Global register Write permission flag (GW) and the Call Depth Counter and Call Depth count Enable field (CDC and CDE). These are described in more detail below.

| 31 |    |    |         |         |    |    | 24 |     |   |     | 16 |  |  |

|----|----|----|---------|---------|----|----|----|-----|---|-----|----|--|--|

|    |    | U  | ser Sta | atus Bi | ts |    |    | Res |   |     |    |  |  |

| 15 | 14 | 13 | 12      | 11      | 10 | 9  | 8  | 7   | 6 |     | 0  |  |  |

| R  | es | PF | s       | l       | 0  | IS | GW | CDE |   | CDC |    |  |  |

| Field | Bits  | Туре | Value | Description                                                                             |

|-------|-------|------|-------|-----------------------------------------------------------------------------------------|

| USB   | 31:24 | rw   |       | User Status Bits                                                                        |

| PRS   | 13:12 | rw   |       | Register Set. This two-bit field selects one of up to four sets of rotection registers. |

|       |       |      | 00    | Protection Register Set 0                                                               |

|       |       |      | 01    | Protection Register Set 1                                                               |

|       |       |      | 10    | Protection Register Set 2                                                               |

|       |       |      | 11    | Protection Register Set 3                                                               |

Architecture Manual

2001-04-30 @ 15:16

| Field | Bits              | Туре | Value                                                              | Description                                                                                                                                                                                                                                              |  |  |  |  |

|-------|-------------------|------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10    | 11:10             | rw   | I/O Privile                                                        | ge. This field selects the I/O privilege mode.                                                                                                                                                                                                           |  |  |  |  |

|       |                   |      | 00                                                                 | User-0                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                   |      | 01                                                                 | User-1                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                   |      | 10                                                                 | Supervisor                                                                                                                                                                                                                                               |  |  |  |  |

|       |                   |      | 11                                                                 | Reserved                                                                                                                                                                                                                                                 |  |  |  |  |

| IS    | 9                 | rw   | Interrupt Stack. This bit reflects the status of the current task. |                                                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 0                                                                  | Current task uses a user stack                                                                                                                                                                                                                           |  |  |  |  |

|       |                   |      | 1                                                                  | Current task uses the global interrupt stack                                                                                                                                                                                                             |  |  |  |  |

| GW    | 8                 | rw   | Global Re<br>global reg                                            | gister Write Permission. This bit enables write permission to the isters                                                                                                                                                                                 |  |  |  |  |

|       |                   |      | 0                                                                  | Write permission to global registers A0, A1, A8, A9 is disabled                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 1                                                                  | Write permission to global registers A0, A1, A8, A9 is enabled                                                                                                                                                                                           |  |  |  |  |

| CDE   | 7                 | rw   | Call Depth                                                         | Count Enable. This bit is the enable for call depth counting.                                                                                                                                                                                            |  |  |  |  |

|       |                   |      | 0                                                                  | Call depth counting is temporarily disabled. It is automatically re-enabled following execution of the next Call instruction.                                                                                                                            |  |  |  |  |

|       | 1                 |      |                                                                    | Call depth counting is enabled. If $CDC = 1111111_2$ , call depth counting is disabled regardless of the setting on this bit.                                                                                                                            |  |  |  |  |

| CDC   | <b>CDC</b> 6:0 rw |      | The first s initial "1" b                                          | Depth Overflow field consists of two variable-width subfields.<br>ubfield is a mask field, consisting of a string of zero or more<br>bits, terminated by the first "0" bit. The remaining bits comprise<br>Id, which constitutes the Call Depth Counter. |  |  |  |  |

|       |                   |      | 0cccccc                                                            | 6-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 10ccccc                                                            | 5-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 110cccc                                                            | 4-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 1110ccc                                                            | 3-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 11110cc                                                            | 2-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 111110c                                                            | 1-bit counter; trap on overflow                                                                                                                                                                                                                          |  |  |  |  |

|       |                   |      | 1111110                                                            | trap every call (call trace mode)                                                                                                                                                                                                                        |  |  |  |  |

|       |                   |      | 1111111                                                            | disable call depth counting                                                                                                                                                                                                                              |  |  |  |  |

The eight most significant bits of the PSW are designated as **User Status Bits**. These bits may be set or cleared as execution side effects of user instructions, typically recording result status. Individual bits can also be used to condition the operation of particular instructions. For example, the ADDX and ADDC instructions use bit 31 to record the carry out from the ADD operation, and the pre-execution value of the bit is reflected in the result of the ADDC instruction.

There are two classes of instructions that employ the user status bits. The first class are the arithmetic instructions that may produce carry and overflow results. The second class are the implementation-specific coprocessor instructions. Instructions in the first class use five of the bits,

with the labels and meanings described in the figure and table below. Instructions in the second class may use any or all of the eight bits, in a manner that is entirely implementation-specific. The RSTV instruction resets the four bits, 30:27, used by the arithmetic instructions to record overflow status. It does not modify any other bits.

| 31 | 30 | 29 | 28 | 27  | 26 | 25  | 24 |

|----|----|----|----|-----|----|-----|----|

| С  | v  | sv | AV | SAV |    | Res |    |

| Field | Bits  | Туре | Value | Description             |

|-------|-------|------|-------|-------------------------|

| С     | 31    | rw   |       | Carry                   |

| V     | 30    | rw   |       | Overflow                |

| sv    | 29    | rw   |       | Sticky Overflow         |

| AV    | 28    | rw   |       | Advance Overflow        |

| SAV   | 27    | rw   |       | Sticky Advance Overflow |

| Res   | 26:24 |      |       | Reserved                |

Bits 23:16 of the PSW are reserved bits, with no defined use in current revisions of the architecture. They read as zero, when the PSW is read via the MFCR instruction after a system reset. Their value, after writing to the PSW via the MTCR instruction, is architecturally undefined.

#### 3.3.3 Previous Context Information Register

Previous Context Information Register (PCXI) contains linkage information to the previous execution context, supporting fast interrupts and automatic context switching. The PCXI is part of a task's state information.

| 31 |      | 24 | 23  | 22 | 21 | 20 | 19 |      | 16 |

|----|------|----|-----|----|----|----|----|------|----|

|    | PCPN |    | PIE | UL |    | -  |    | PCXS |    |

| 15 |      |    |     |    |    |    |    |      | 0  |

|    |      | PC | хо  |    |    |    |    |      |    |

## Core Registers Context Management Registers

2001-04-30 @ 15:16

| Field | Bits  | Туре | Value | Description                                                                                                                                                                                                                                                                        |

|-------|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCPN  | 31:24 | rw   |       | Previous CPU Priority Number. This field contains the priority level number of the interrupted task.                                                                                                                                                                               |

| PIE   | 23    | rw   |       | Previous Interrupt Enable. This bit indicates the state of the interrupt enable bit (ICR.IE) for the interrupted task.                                                                                                                                                             |

| UL    | 22    | rw   |       | Upper/Lower Context Tag. The U/L context tag bit identifies<br>the type of context saved. A one indicates upper context; a<br>zero indicates lower context. If the type does not match the<br>type expected when a context restore operation is performed,<br>a trap is generated. |

| PCXS  | 19:16 | rw   |       | PCX Segment Address. This field contains the segment address portion of the PCX.                                                                                                                                                                                                   |

| РСХО  | 15:0  | rw   |       | Previous Context Pointer Offset Field. The PCXO and PCXS fields form the pointer PCX, which points to the CSA of the previous context.                                                                                                                                             |

#### 3.4 Context Management Registers

This section describes the context management registers, which are comprised of 3 pointers that handle context management and are used during context save/restore operations (Table 3-2).

#### Table 3-2 Context Management Registers

| Register | Category                                              |  |

|----------|-------------------------------------------------------|--|

| FCX      | Free CSA List Head Pointer                            |  |

| PCX      | Previous Context Pointer (contained in register PCXI) |  |

| LCX      | Free CSA List Limit Pointer                           |  |

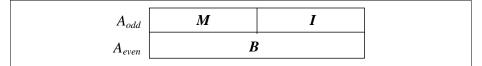

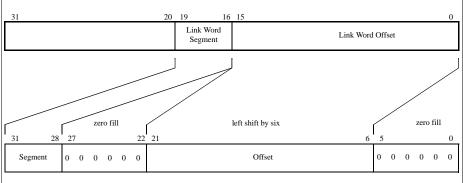

Each pointer consists of 2 fields: a 16-bit offset and a 4-bit segment specifier. Figure 3-2 shows how the effective address of a CSA is generated using the 2 fields. A Context Save Area (CSA) is an address range containing 16 word locations (64 bytes), which is the space required to save 1 upper or 1 lower context. Incrementing the pointer offset value by 1 always increments the effective address to the address that is 16 word locations above the previous one. The total usable range in each address segment for CSAs is 4 MBytes, resulting in storage space for 64 K CSAs.

#### Figure 3-2 Generation of the Effective Address for the Context Save Areas

Note that the effective address is a physical memory address which must map to local data or cached memory. Address ranges not covered by physical memories could lead to unexpected results. Segments 14 and 15, which are reserved for external and internal peripherals, should also not be used for CSAs.

### 3.4.1 Free CSA List Head Pointer

The Free CSA List Head Pointer (FCX) register holds the free CSA list head pointer, which always points to an available CSA.

| - | FCXS |  |

|---|------|--|

15

| FCXO |  |

|------|--|

|      |  |

|      |  |

| Field | Bits  | Туре | Value | Description                                                                                                               |

|-------|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------|

| FCXS  | 19:16 | rw   |       | FCX Segment Address Field. This field is used in conjunction with the FCXO field.                                         |

| FCXO  | 15:0  | rw   |       | FCX Offset Address Field. The FCXO and FCXS fields together form the FCX pointer, which points to the next available CSA. |

0

#### 3.4.2 Previous Context Pointer

The Previous Context Pointer (PCX) holds the address of the CSA of the previous task. PCX is part of PCXI. It is shown below for easy reference. The bits not relevant to the pointer function are shaded.

| 31 |      | 24 | 23  | 22 | 21 | 20 | 19 |      | 16 |

|----|------|----|-----|----|----|----|----|------|----|

|    | PCPN |    | PIE | UL |    | -  |    | PCXS |    |

| 15 |      |    |     |    |    |    |    |      | 0  |

|    |      | PC | хо  |    |    |    |    |      |    |

| Field | Bits  | Туре | Value | Description                                                                                                                            |

|-------|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| PCXS  | 19:16 | rw   |       | PCX Segment Address Field. This field is used in<br>conjunction with the PCXO field.                                                   |

| РСХО  | 15:0  | rw   |       | Previous Context Pointer Offset Field. The PCXO and PCXS fields form the pointer PCX, which points to the CSA of the previous context. |

#### 3.4.3 Free CSA List Limit Pointer

The Free CSA List Limit Pointer (LCX) register is used to recognize impending CSA list underflows. If the new value of FCX resulting after a CALL or interrupt matches the limit value, the "free context depletion" condition is recognized, which triggers an FCD trap immediately after completion of the call or interrupt entry sequence. It is important to see the FCD trap description for datails on the use and setting of LCX.

#### LCX Free CSA List Limit Pointer

| 31 | 20 | 19   | 16 |

|----|----|------|----|

|    |    | LCXS |    |

| 15 |    |      | 0  |

LCXO

15

| Field | Bits  | Туре | Value | Description                                                                                              |

|-------|-------|------|-------|----------------------------------------------------------------------------------------------------------|

| LCXS  | 19:16 | rw   |       | LCX Segment Address. This field is used in conjunction with the LCXO field.                              |

| LCXO  | 15:0  | rw   |       | LCX Offset Field. The LCXO and LCXS fields form the pointer LCX, which points to the last available CSA. |

#### 3.5 Stack Management

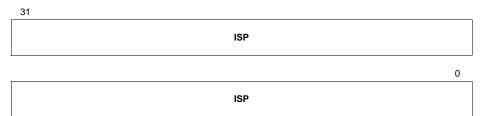

The stack management in the TriCore architecture supports a user stack and an interrupt stack. Address register A10, the Interrupt Stack Pointer (ISP), and a PSW bit are involved in the management of the stack.

#### A10/SP

#### Address Register A10/Stack Pointer

31

A10/SP

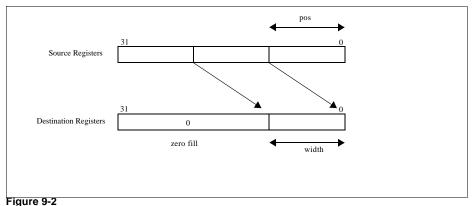

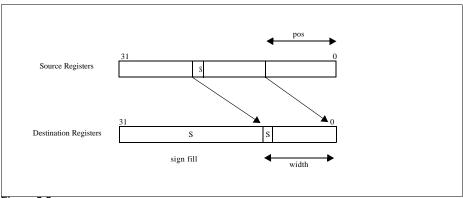

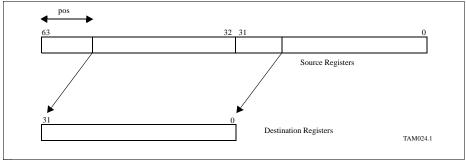

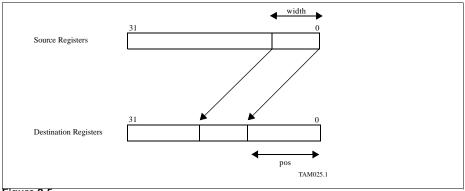

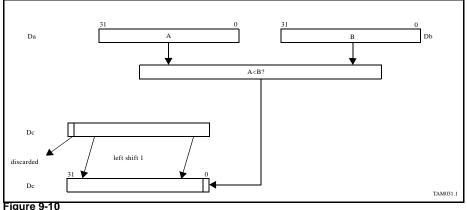

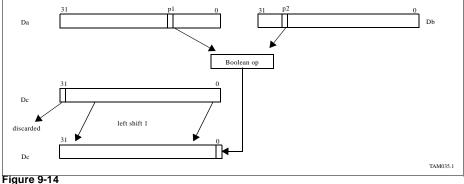

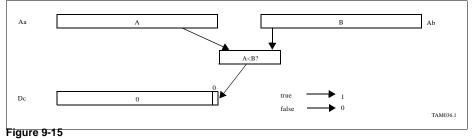

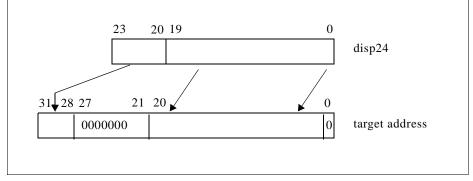

A10/SP